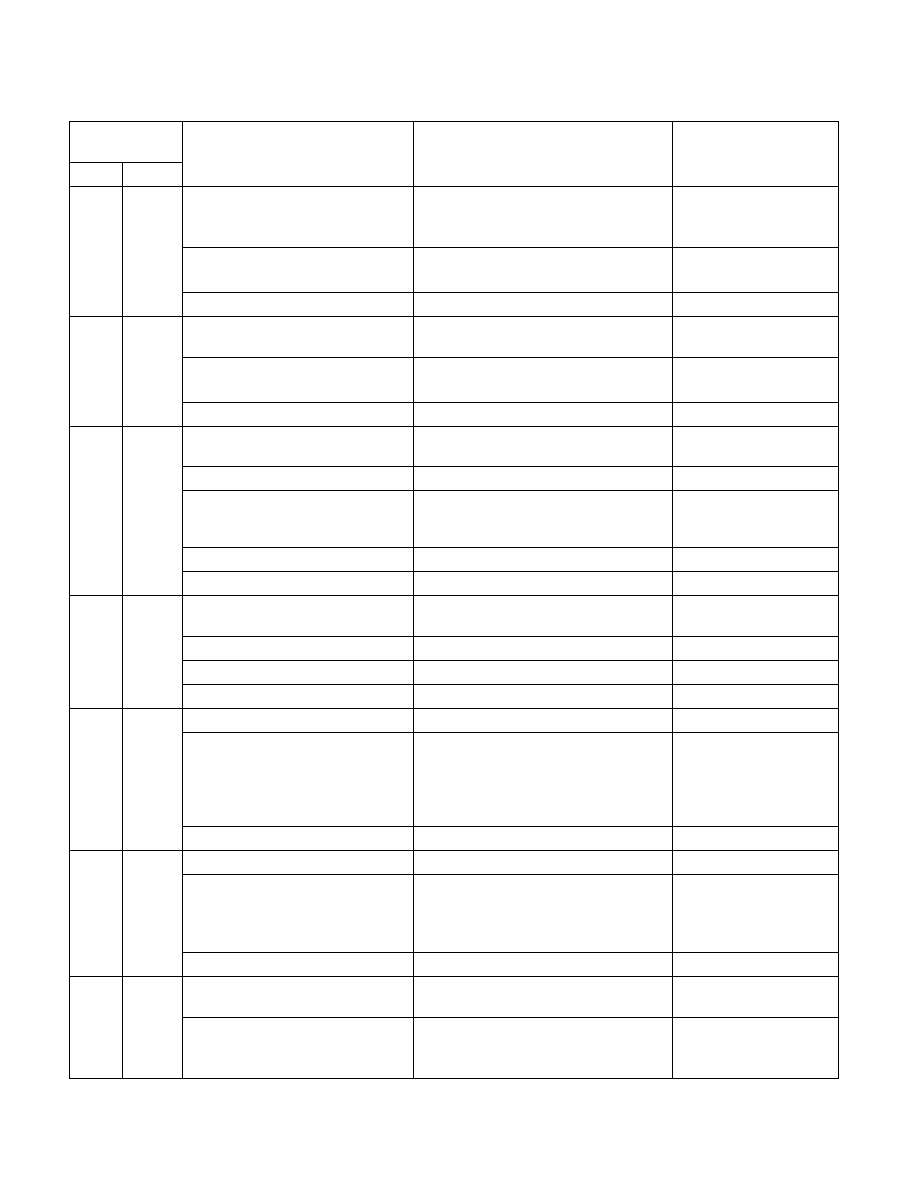

Vol. 3C 35-41

MODEL-SPECIFIC REGISTERS (MSRS)

D10H

3344

IA32_L2_MASK_0

L2 CAT Mask for COS0 (R/W)

If (CPUID.(EAX=10H,

ECX=0H):EBX[2] != 0)

31:0

Capacity Bit Mask (R/W)

63:32

Reserved.

D10H+

n

3344+n IA32_L2_MASK_n

L2 CAT Mask for COSn (R/W)

n = CPUID.(EAX=10H,

ECX=2H):EDX[15:0]

31:0

Capacity Bit Mask (R/W)

63:32

Reserved.

D90H

3472

IA32_BNDCFGS

Supervisor State of MPX Configuration.

(R/W)

If (CPUID.(EAX=07H,

ECX=0H):EBX[14] = 1)

0

EN: Enable Intel MPX in supervisor mode

1

BNDPRESERVE: Preserve the bounds

registers for near branch instructions in the

absence of the BND prefix

11:2

Reserved, must be 0

63:12

Base Address of Bound Directory.

DA0H

3488

IA32_XSS

Extended Supervisor State Mask (R/W)

If( CPUID.(0DH, 1):EAX.[3]

= 1

7:0

Reserved

8

Trace Packet Configuration State (R/W)

63:9

Reserved.

DB0H

3504

IA32_PKG_HDC_CTL

Package Level Enable/disable HDC (R/W) If CPUID.06H:EAX.[13] = 1

0

HDC_Pkg_Enable (R/W)

Force HDC idling or wake up HDC-idled

logical processors in the package. See

Section 14.5.2, “Package level Enabling

If CPUID.06H:EAX.[13] = 1

63:1

Reserved.

DB1H

3505

IA32_PM_CTL1

Enable/disable HWP (R/W)

If CPUID.06H:EAX.[13] = 1

0

HDC_Allow_Block (R/W)

Allow/Block this logical processor for

package level HDC control. See Section

If CPUID.06H:EAX.[13] = 1

63:1

Reserved.

DB2H

3506

IA32_THREAD_STALL

Per-Logical_Processor HDC Idle

Residency (R/0)

If CPUID.06H:EAX.[13] = 1

63:0

Stall_Cycle_Cnt (R/W)

Stalled cycles due to HDC forced idle on this

logical processor. See Section 14.5.4.1

If CPUID.06H:EAX.[13] = 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal