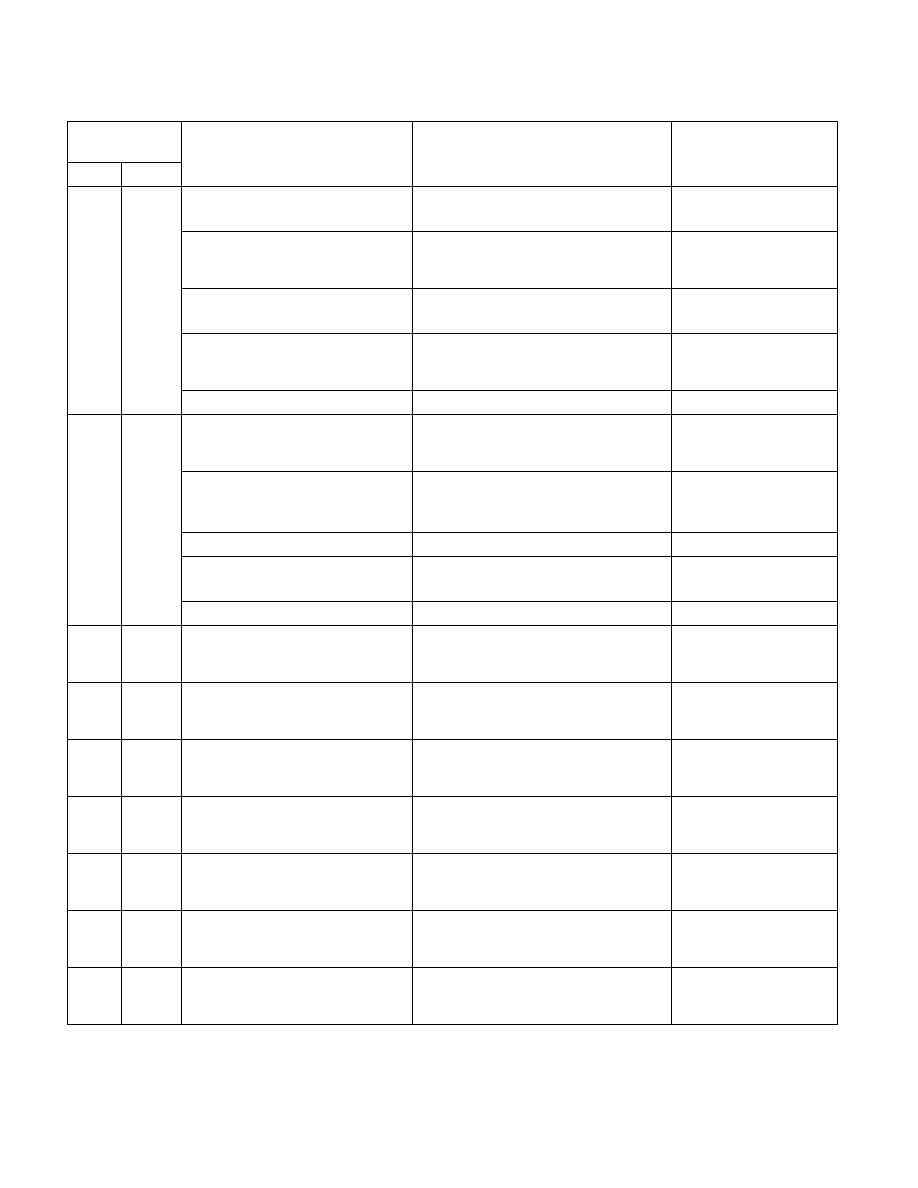

35-36 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

23:16

Desired_Performance

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[7] = 1

31:24

Energy_Performance_Preference

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[7] = 1

&& CPUID.06H:EAX.[10] =

1

41:32

Activity_Window

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[7] = 1

&& CPUID.06H:EAX.[9] = 1

42

Package_Control

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[7] = 1

&& CPUID.06H:EAX.[11] =

1

63:43

Reserved.

777H

1911

IA32_HWP_STATUS

Log bits indicating changes to

Guaranteed & excursions to Minimum

(R/W)

If CPUID.06H:EAX.[7] = 1

0

Guaranteed_Performance_Change

(R/WC0).

See Section 14.4.5, “HWP Feedback”

If CPUID.06H:EAX.[7] = 1

1

Reserved.

2

Excursion_To_Minimum (R/WC0).

See Section 14.4.5, “HWP Feedback”

If CPUID.06H:EAX.[7] = 1

63:3

Reserved.

802H

2050

IA32_X2APIC_APICID

x2APIC ID Register (R/O)

See x2APIC Specification

If CPUID.01H:ECX[21] = 1

&& IA32_APIC_BASE.[10]

= 1

803H

2051

IA32_X2APIC_VERSION

x2APIC Version Register (R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

808H

2056

IA32_X2APIC_TPR

x2APIC Task Priority Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

80AH

2058

IA32_X2APIC_PPR

x2APIC Processor Priority Register (R/O) If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

80BH

2059

IA32_X2APIC_EOI

x2APIC EOI Register (W/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

80DH

2061

IA32_X2APIC_LDR

x2APIC Logical Destination Register

(R/O)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

80FH

2063

IA32_X2APIC_SIVR

x2APIC Spurious Interrupt Vector

Register (R/W)

If CPUID.01H:ECX.[21] = 1

&& IA32_APIC_BASE.[10]

= 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal