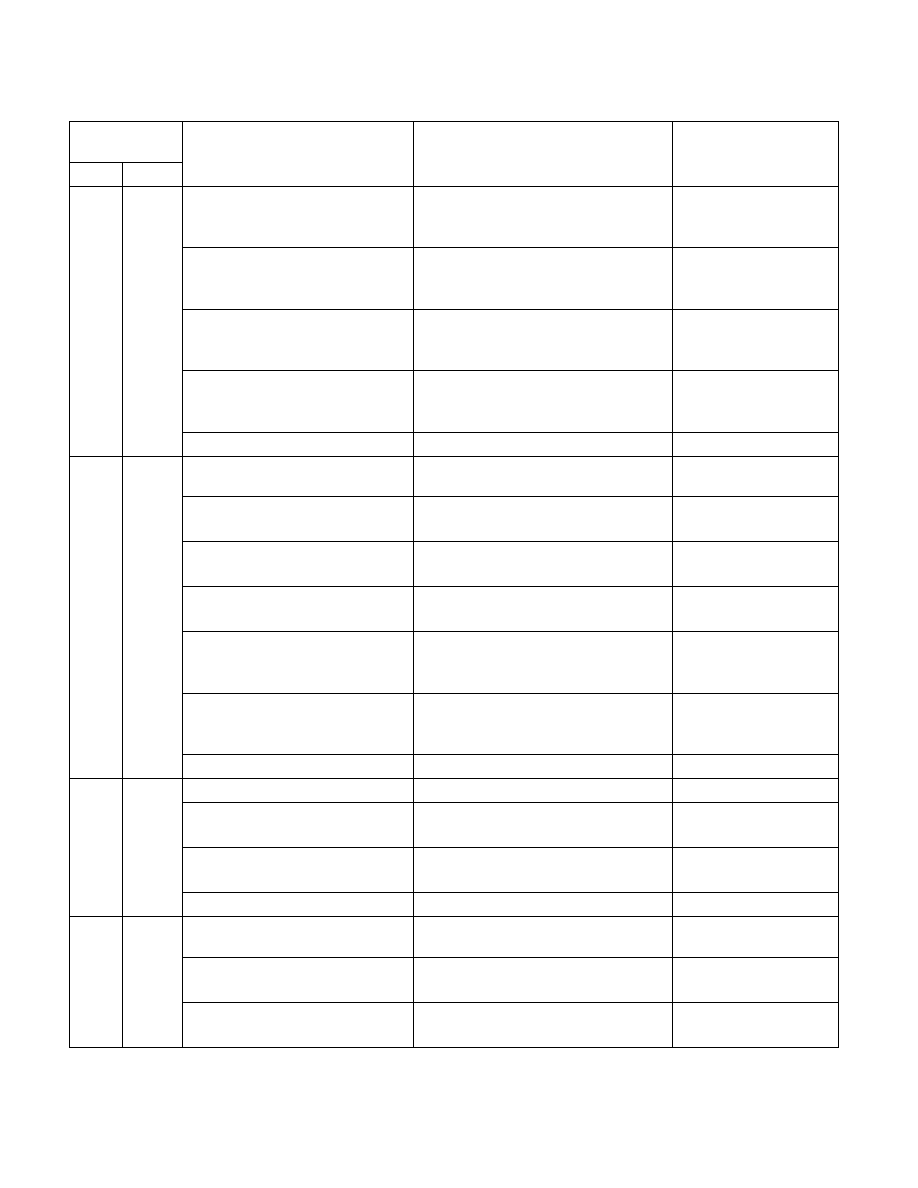

Vol. 3C 35-35

MODEL-SPECIFIC REGISTERS (MSRS)

7:0

Highest_Performance

See Section 14.4.3, “HWP Performance

Range and Dynamic Capabilities”

If CPUID.06H:EAX.[7] = 1

15:8

Guaranteed_Performance

See Section 14.4.3, “HWP Performance

Range and Dynamic Capabilities”

If CPUID.06H:EAX.[7] = 1

23:16

Most_Efficient_Performance

See Section 14.4.3, “HWP Performance

Range and Dynamic Capabilities”

If CPUID.06H:EAX.[7] = 1

31:24

Lowest_Performance

See Section 14.4.3, “HWP Performance

Range and Dynamic Capabilities”

If CPUID.06H:EAX.[7] = 1

63:32

Reserved.

772H

1906

IA32_HWP_REQUEST_PKG

Power Management Control Hints for All

Logical Processors in a Package (R/W)

If CPUID.06H:EAX.[11] = 1

7:0

Minimum_Performance

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[11] = 1

15:8

Maximum_Performance

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[11] = 1

23:16

Desired_Performance

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[11] = 1

31:24

Energy_Performance_Preference

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[11] = 1

&&

CPUID.06H:EAX.[10] = 1

41:32

Activity_Window

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[11] = 1

&&

CPUID.06H:EAX.[9] = 1

63:42

Reserved.

773H

1907

IA32_HWP_INTERRUPT

Control HWP Native Interrupts (R/W)

If CPUID.06H:EAX.[8] = 1

0

EN_Guaranteed_Performance_Change.

See Section 14.4.6, “HWP Notifications”

If CPUID.06H:EAX.[8] = 1

1

EN_Excursion_Minimum.

See Section 14.4.6, “HWP Notifications”

If CPUID.06H:EAX.[8] = 1

63:2

Reserved.

774H

1908

IA32_HWP_REQUEST

Power Management Control Hints to a

Logical Processor (R/W)

If CPUID.06H:EAX.[7] = 1

7:0

Minimum_Performance

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[7] = 1

15:8

Maximum_Performance

See Section 14.4.4, “Managing HWP”

If CPUID.06H:EAX.[7] = 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal