Vol. 3C 34-9

SYSTEM MANAGEMENT MODE

For systems that explicitly flush the caches upon entering SMM (the third method described above), the cache flush

can be accomplished by asserting the FLUSH# pin at the same time as the request to enter SMM (generally initi-

ated by asserting the SMI# pin). The priorities of the FLUSH# and SMI# pins are such that the FLUSH# is serviced

first. To guarantee this behavior, the processor requires that the following constraints on the interaction of FLUSH#

and SMI# be met. In a system where the FLUSH# and SMI# pins are synchronous and the set up and hold times

are met, then the FLUSH# and SMI# pins may be asserted in the same clock. In asynchronous systems, the

FLUSH# pin must be asserted at least one clock before the SMI# pin to guarantee that the FLUSH# pin is serviced

first.

Upon leaving SMM (for systems that explicitly flush the caches), the WBINVD instruction should be executed prior

to leaving SMM to flush the caches.

NOTES

In systems based on the Pentium processor that use the FLUSH# pin to write back and invalidate

cache contents before entering SMM, the processor will prefetch at least one cache line in between

when the Flush Acknowledge cycle is run and the subsequent recognition of SMI# and the assertion

of SMIACT#.

It is the obligation of the system to ensure that these lines are not cached by returning KEN#

inactive to the Pentium processor.

34.4.2.1 System Management Range Registers (SMRR)

SMI handler code and data stored by SMM code resides in SMRAM. The SMRR interface is an enhancement in Intel

64 architecture to limit cacheable reference of addresses in SMRAM to code running in SMM. The SMRR interface

can be configured only by code running in SMM. Details of SMRR is described in Section 11.11.2.4.

34.5

SMI HANDLER EXECUTION ENVIRONMENT

Section 34.5.1 describes the initial execution environment for an SMI handler. An SMI handler may re-configure its

execution environment to other supported operating modes. Section 34.5.2 discusses modifications an SMI

handler can make to its execution environment.

34.5.1

Initial SMM Execution Environment

After saving the current context of the processor, the processor initializes its core registers to the values shown in

Table 34-4. Upon entering SMM, the PE and PG flags in control register CR0 are cleared, which places the processor

in an environment similar to real-address mode. The differences between the SMM execution environment and the

real-address mode execution environment are as follows:

•

The addressable address space ranges from 0 to FFFFFFFFH (4 GBytes).

•

The normal 64-KByte segment limit for real-address mode is increased to 4 GBytes.

•

The default operand and address sizes are set to 16 bits, which restricts the addressable SMRAM address space

to the 1-MByte real-address mode limit for native real-address-mode code. However, operand-size and

address-size override prefixes can be used to access the address space beyond the 1-MByte.

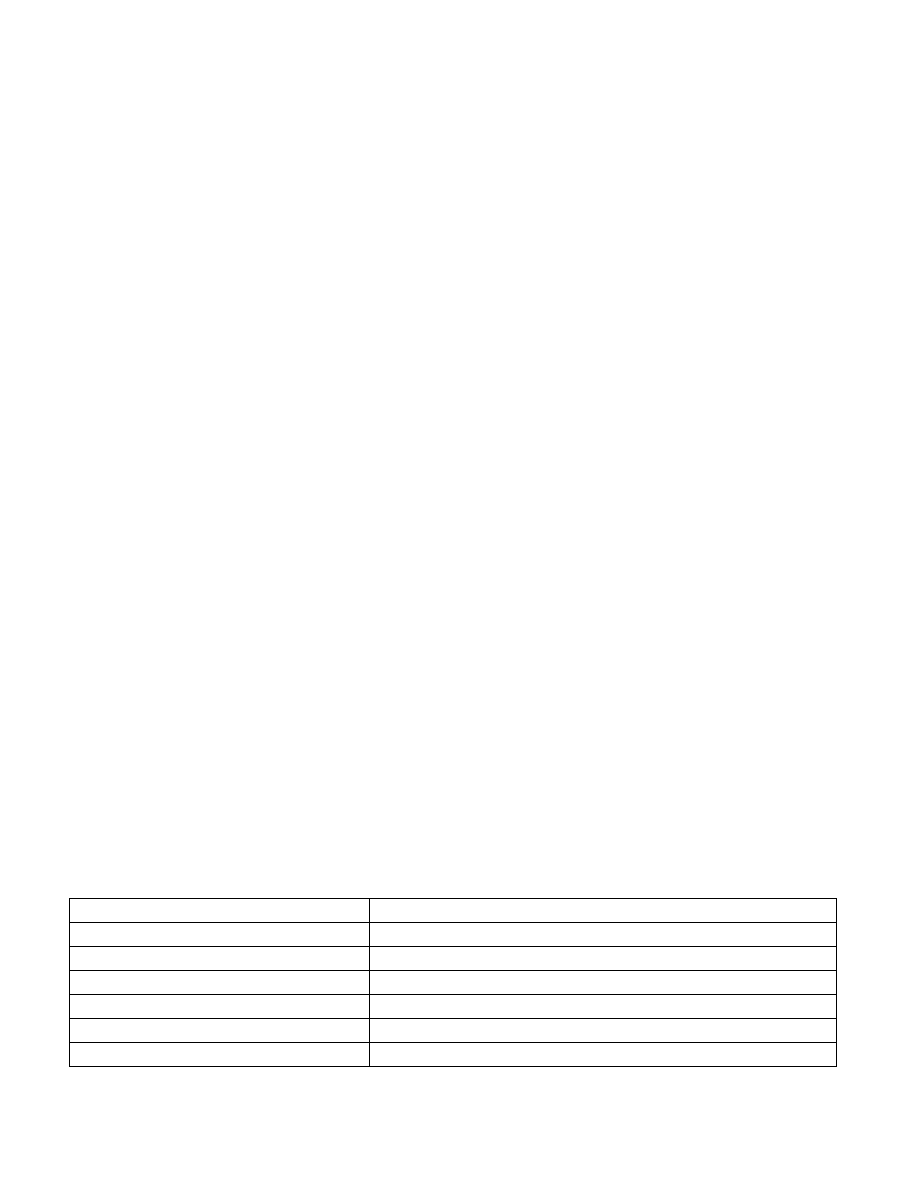

Table 34-4. Processor Register Initialization in SMM

Register

Contents

General-purpose registers

Undefined

EFLAGS

00000002H

EIP

00008000H

CS selector

SMM Base shifted right 4 bits (default 3000H)

CS base

SMM Base (default 30000H)

DS, ES, FS, GS, SS Selectors

0000H