4-20 Vol. 3A

PAGING

from CR3[11:0] to 000H (see also Section 4.10.4.1). In addition, the logical processor subsequently determines

the memory type used to access the PML4 table using CR3.PWT and CR3.PCD, which had been bits 4:3 of the PCID.

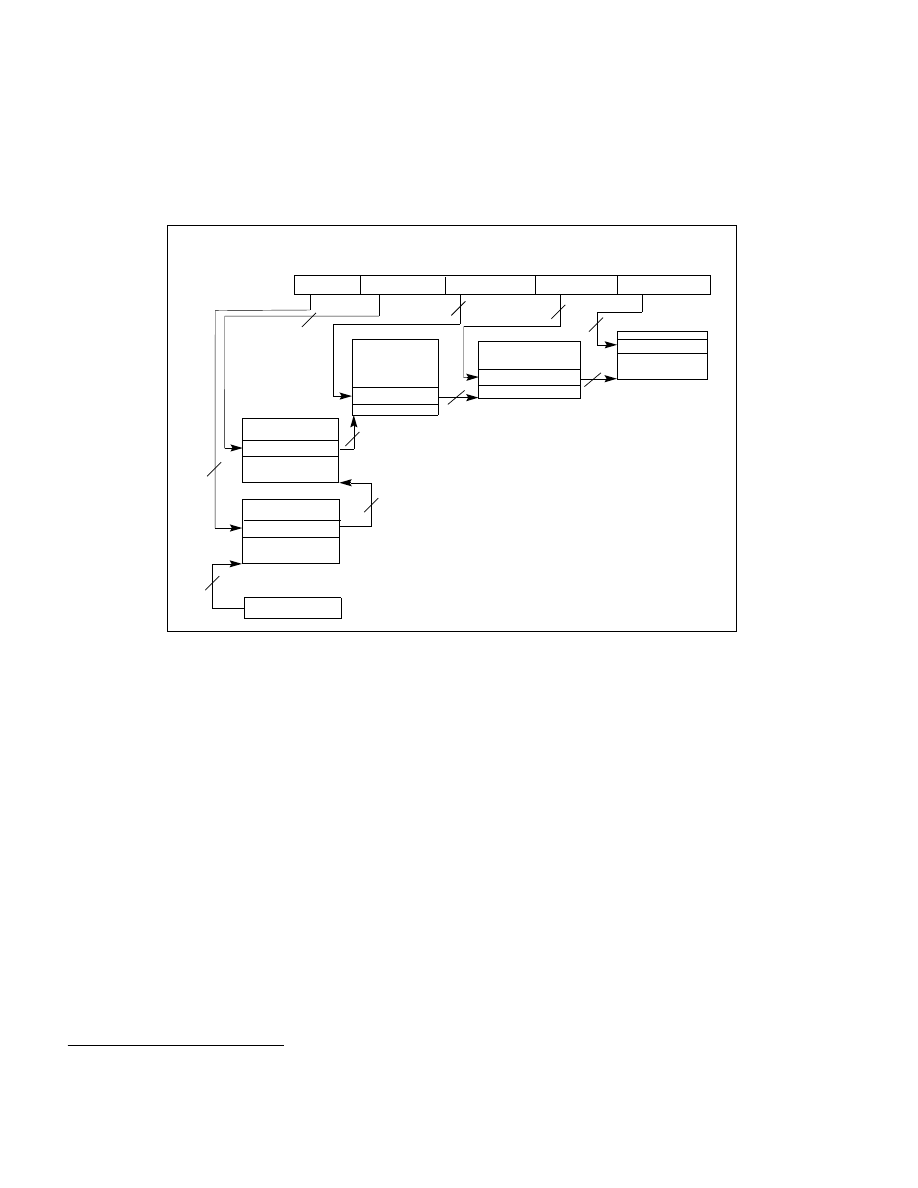

IA-32e paging may map linear addresses to 4-KByte pages, 2-MByte pages, or 1-GByte pages.

1

trates the translation process when it produces a 4-KByte page; Figure 4-9 covers the case of a 2-MByte page, and

Figure 4-10 the case of a 1-GByte page.

1. Not all processors support 1-GByte pages; see Section 4.1.4.

Figure 4-8. Linear-Address Translation to a 4-KByte Page using IA-32e Paging

Directory Ptr

PTE

Linear Address

Page Table

PDPTE

CR3

39 38

Pointer Table

9

9

40

12

9

40

4-KByte Page

Offset

Physical Addr

PDE with PS=0

Table

0

11

12

20

21

Directory

30 29

Page-Directory-

Page-Directory

PML4

47

9

PML4E

40

40

40