4-18 Vol. 3A

PAGING

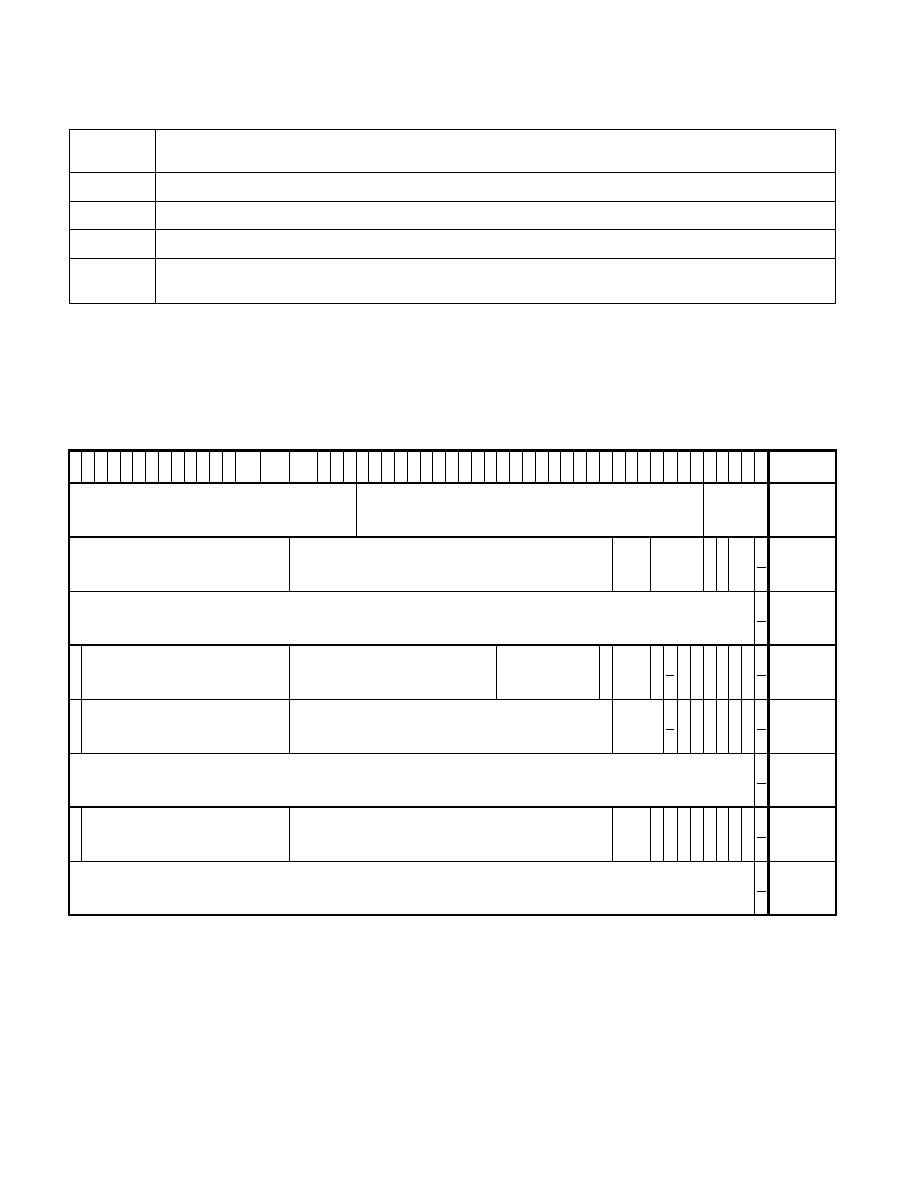

Figure 4-7 gives a summary of the formats of CR3 and the paging-structure entries with PAE paging. For the paging

structure entries, it identifies separately the format of entries that map pages, those that reference other paging

structures, and those that do neither because they are “not present”; bit 0 (P) and bit 7 (PS) are highlighted

because they determine how a paging-structure entry is used.

11:9

Ignored

(M–1):12

Physical address of the 4-KByte page referenced by this entry

62:M

Reserved (must be 0)

63 (XD)

If IA32_EFER.NXE = 1, execute-disable (if 1, instruction fetches are not allowed from the 4-KByte page controlled by

this entry; see Section 4.6); otherwise, reserved (must be 0)

NOTES:

1. See Section 4.1.4 for how to determine whether the PAT is supported.

6

3

6

2

6

1

6

0

5

9

5

8

5

7

5

6

5

5

5

4

5

3

5

2

5

1

M

1

NOTES:

1. M is an abbreviation for MAXPHYADDR.

M-1

3

2

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Ignored

2

2. CR3 has 64 bits only on processors supporting the Intel-64 architecture. These bits are ignored with PAE paging.

Address of page-directory-pointer table

Ignored

CR3

Reserved

3

3. Reserved fields must be 0.

Address of page directory

Ign.

Rsvd.

P

C

D

P

W

T

Rs

vd 1

PDPTE:

present

Ignored

0

PDTPE:

not

present

X

D

4

4. If IA32_EFER.NXE = 0 and the P flag of a PDE or a PTE is 1, the XD flag (bit 63) is reserved.

Reserved

Address of

2MB page frame

Reserved

P

A

T

Ign. G 1 D A

P

C

D

P

W

T

U

/S

R

/

W

1

PDE:

2MB

page

X

D

Reserved

Address of page table

Ign.

0

I

g

n

A

P

C

D

P

W

T

U

/S

R

/

W

1

PDE:

page

table

Ignored

0

PDE:

not

present

X

D

Reserved

Address of 4KB page frame

Ign. G

P

A

T

D A

P

C

D

P

W

T

U

/S

R

/

W

1

PTE:

4KB

page

Ignored

0

PTE:

not

present

Figure 4-7. Formats of CR3 and Paging-Structure Entries with PAE Paging

Table 4-11. Format of a PAE Page-Table Entry that Maps a 4-KByte Page (Contd.)

Bit

Position(s)

Contents