30-6 Vol. 3C

VMX INSTRUCTION REFERENCE

INVVPIDтАФ Invalidate Translations Based on VPID

Description

Invalidates mappings in the translation lookaside buffers (TLBs) and paging-structure caches based on virtual-

processor identifier (VPID). (See Chapter 28, тАЬVMX Support for Address TranslationтАЭ.) Invalidation is based on

the INVVPID type specified in the register operand and the INVVPID descriptor specified in the memory

operand.

Outside IA-32e mode, the register operand is always 32 bits, regardless of the value of CS.D; in 64-bit mode, the

register operand has 64 bits (the instruction cannot be executed in compatibility mode).

The INVVPID types supported by a logical processors are reported in the IA32_VMX_EPT_VPID_CAP MSR (see

Appendix A, тАЬVMX Capability Reporting FacilityтАЭ). There are four INVVPID types currently defined:

тАв

Individual-address invalidation: If the INVVPID type is 0, the logical processor invalidates mappings for the

linear address and VPID specified in the INVVPID descriptor. In some cases, it may invalidate mappings for

other linear addresses (or other VPIDs) as well.

тАв

Single-context invalidation: If the INVVPID type is 1, the logical processor invalidates all mappings tagged with

the VPID specified in the INVVPID descriptor. In some cases, it may invalidate mappings for other VPIDs as

well.

тАв

All-contexts invalidation: If the INVVPID type is 2, the logical processor invalidates all mappings tagged with all

VPIDs except VPID 0000H. In some cases, it may invalidate translations with VPID 0000H as well.

тАв

Single-context invalidation, retaining global translations: If the INVVPID type is 3, the logical processor

invalidates all mappings tagged with the VPID specified in the INVVPID descriptor except global translations. In

some cases, it may invalidate global translations (and mappings with other VPIDs) as well. See the тАЬCaching

Translation InformationтАЭ section in Chapter 4 of the IA-32 Intel Architecture Software DeveloperтАЩs Manual,

Volumes 3A for information about global translations.

If an unsupported INVVPID type is specified, the instruction fails.

INVVPID invalidates all the specified mappings for the indicated VPID(s) regardless of the EPTP and PCID values

with which those mappings may be associated.

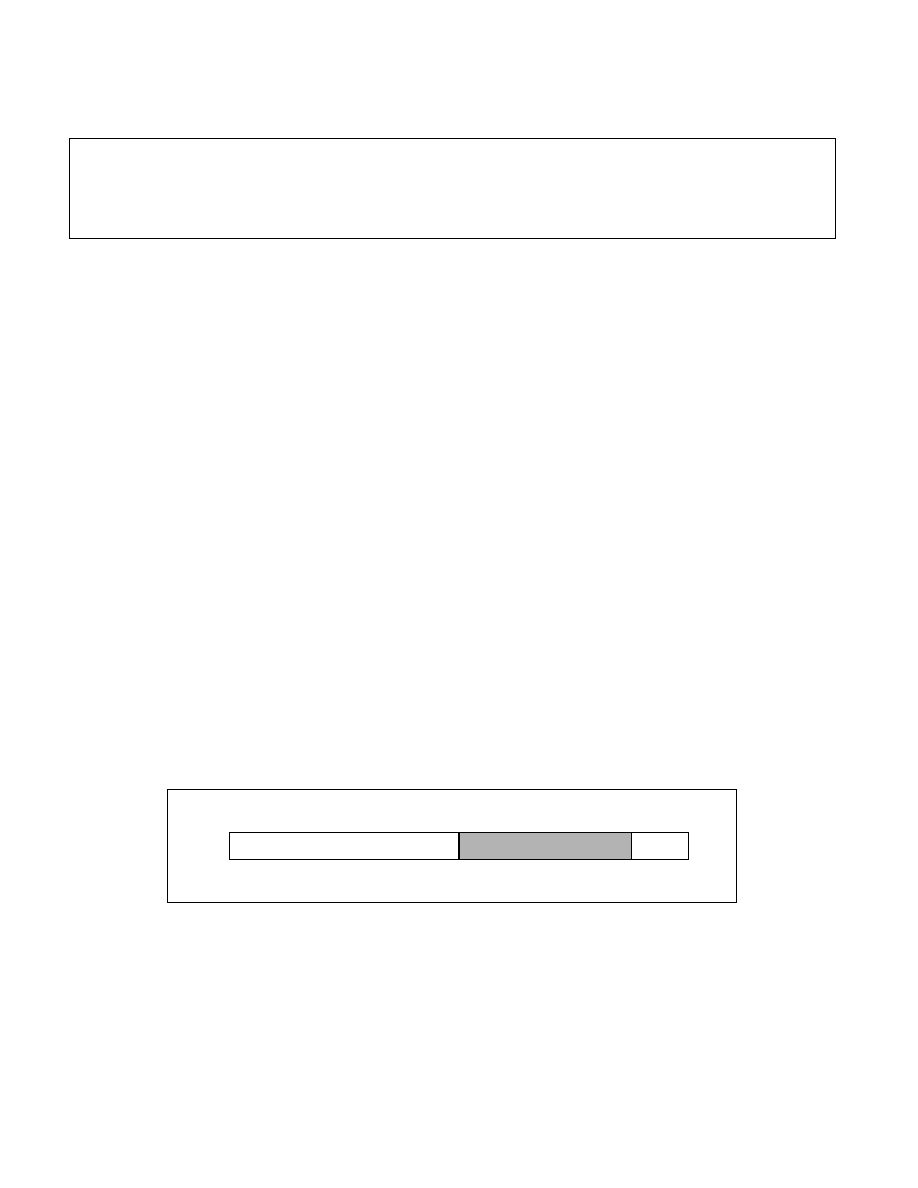

The INVVPID descriptor comprises 128 bits and consists of a VPID and a linear address as shown in Figure 30-2.

Opcode

Instruction

Description

66 0F 38 81

INVVPID r64, m128

Invalidates entries in the TLBs and paging-structure caches based on VPID (in

64-bit mode)

66 0F 38 81

INVVPID r32, m128

Invalidates entries in the TLBs and paging-structure caches based on VPID

(outside 64-bit mode)

Figure 30-2. INVVPID Descriptor

127

64 63

0

15

16

Reserved (must be zero)

Linear Address

VPID