28-6 Vol. 3C

VMX SUPPORT FOR ADDRESS TRANSLATION

— Bits 51:12 are from the EPT PTE.

— Bits 11:0 are from the original guest-physical address.

The format of an EPT PTE is given in Table 28-6.

If bits 2:0 of an EPT paging-structure entry are all 0, the entry is not present. The processor ignores bits 62:3 and

uses the entry neither to reference another EPT paging-structure entry nor to produce a physical address. A refer-

ence using a guest-physical address whose translation encounters an EPT paging-structure that is not present

causes an EPT violation (see Section 28.2.3.2). (If the “EPT-violation #VE” VM-execution control is 1, the EPT viola-

tion is convertible to a virtualization exception only if bit 63 is 0; see Section 25.5.6.1. If the “EPT-violation #VE”

VM-execution control is 0, this bit is ignored.)

The discussion above describes how the EPT paging structures reference each other and how the logical processor

traverses those structures when translating a guest-physical address. It does not cover all details of the translation

process. Additional details are provided as follows:

•

Situations in which the translation process may lead to VM exits (sometimes before the process completes) are

described in Section 28.2.3.

•

Interactions between the EPT translation mechanism and memory typing are described in Section 28.2.6.

Figure 28-1 gives a summary of the formats of the EPTP and the EPT paging-structure entries. For the EPT paging

structure entries, it identifies separately the format of entries that map pages, those that reference other EPT

paging structures, and those that do neither because they are “not present”; bits 2:0 and bit 7 are highlighted

because they determine how a paging-structure entry is used.

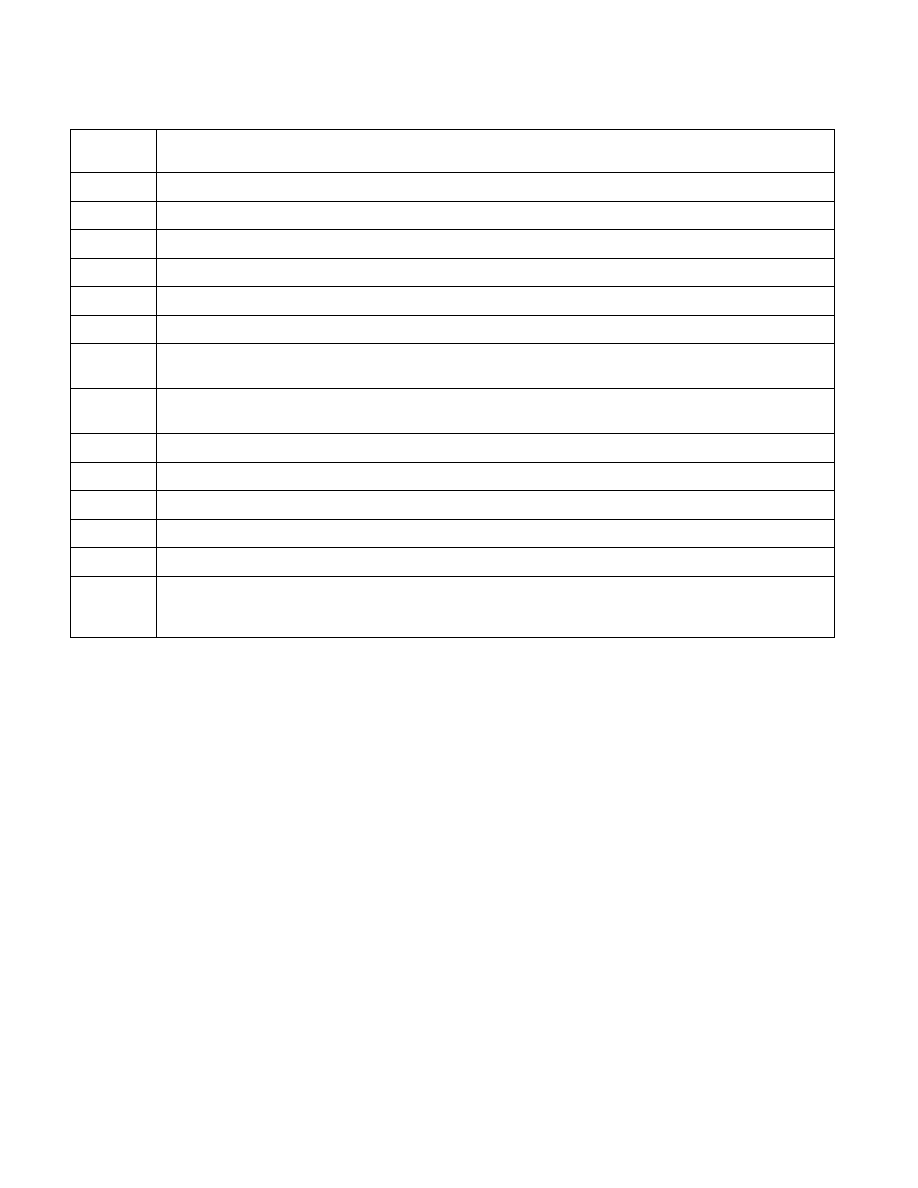

Table 28-4. Format of an EPT Page-Directory Entry (PDE) that Maps a 2-MByte Page

Bit

Position(s)

Contents

0

Read access; indicates whether reads are allowed from the 2-MByte page referenced by this entry

1

Write access; indicates whether writes are allowed to the 2-MByte page referenced by this entry

2

Execute access; indicates whether instruction fetches are allowed from the 2-MByte page referenced by this entry

5:3

EPT memory type for this 2-MByte page (see Section 28.2.6)

6

Ignore PAT memory type for this 2-MByte page (see Section 28.2.6)

7

Must be 1 (otherwise, this entry references an EPT page table)

8

If bit 6 of EPTP is 1, accessed flag for EPT; indicates whether software has accessed the 2-MByte page referenced

by this entry (see Section 28.2.4). Ignored if bit 6 of EPTP is 0

9

If bit 6 of EPTP is 1, dirty flag for EPT; indicates whether software has written to the 2-MByte page referenced by

this entry (see Section 28.2.4). Ignored if bit 6 of EPTP is 0

11:10

Ignored

20:12

Reserved (must be 0)

(N–1):21

Physical address of the 2-MByte page referenced by this entry

1

51:N

Reserved (must be 0)

62:52

Ignored

63

Suppress #VE. If the “EPT-violation #VE” VM-execution control is 1, EPT violations caused by accesses to this page

are convertible to virtualization exceptions only if this bit is 0 (see Section 25.5.6.1). If “EPT-violation #VE” VM-

execution control is 0, this bit is ignored.

NOTES:

1. N is the physical-address width supported by the logical processor.