Vol. 3C 28-9

VMX SUPPORT FOR ADDRESS TRANSLATION

•

The access is a data write and bit 1 was clear in any of the EPT paging-structure entries used to translate the

guest-physical address. Writes by the logical processor to guest paging structures to update accessed and dirty

flags are considered to be data writes.

If bit 6 of the EPT pointer (EPTP) is 1 (enabling accessed and dirty flags for EPT), processor accesses to guest

paging-structure entries are treated as writes with regard to EPT violations. Thus, if bit 1 is clear in any of the

EPT paging-structure entries used to translate the guest-physical address of a guest paging-structure entry, an

attempt to use that entry to translate a linear address causes an EPT violation.

(This does not apply to loads of the PDPTE registers by the MOV to CR instruction for PAE paging; see Section

4.4.1. Those loads of guest PDPTEs are treated as reads and do not cause EPT violations due to a guest-

physical address not being writable.)

•

The access is an instruction fetch and bit 2 was clear in any of the EPT paging-structure entries used to

translate the guest-physical address.

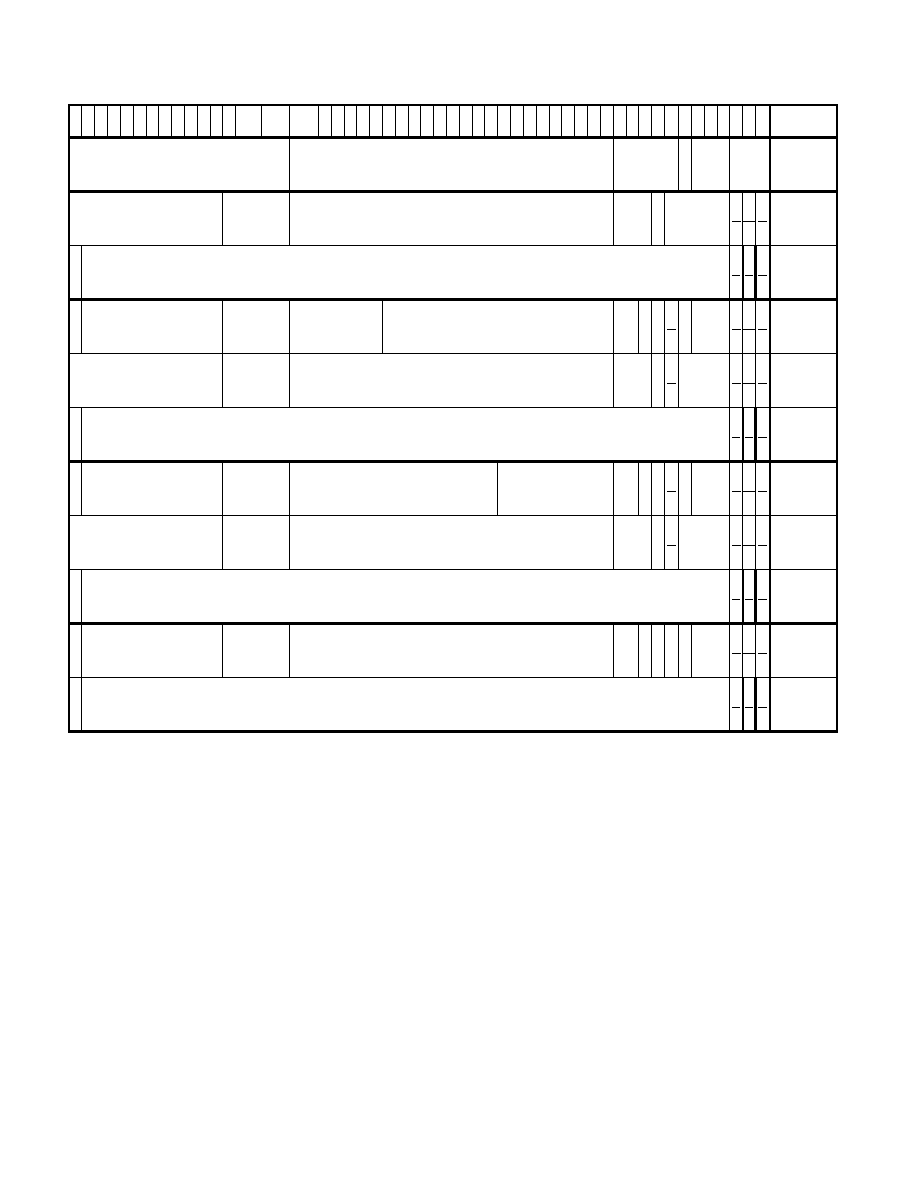

6

3

6

2

6

1

6

0

5

9

5

8

5

7

5

6

5

5

5

4

5

3

5

2

5

1

M

1

M-1

3

2

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Reserved

Address of EPT PML4 table

Rsvd.

A

/

D

EPT

PWL–

1

EPT

PS

MT

EPTP

2

Ignored

Rsvd.

Address of EPT page-directory-pointer table

Ign. A Reserved X W R PML4E:

present

S

V

E

3

Ignored

0 0 0

PML4E:

not

present

S

V

E

Ignored

Rsvd.

Physical

address of

1GB page

Reserved

Ign. D A 1

I

P

A

T

EPT

MT X W R

PDPTE:

1GB

page

Ignored

Rsvd.

Address of EPT page directory

Ign. A 0 Rsvd. X W R

PDPTE:

page

directory

S

V

E

Ignored

0 0 0

PDTPE:

not

present

S

V

E

Ignored

Rsvd.

Physical address

of 2MB page

Reserved

Ign. D A 1

I

P

A

T

EPT

MT X W R

PDE:

2MB

page

Ignored

Rsvd.

Address of EPT page table

Ign. A 0 Rsvd. X W R

PDE:

page

table

S

V

E

Ignored

0 0 0

PDE:

not

present

S

V

E

Ignored

Rsvd.

Physical address of 4KB page

Ign. D A

I

g

n

I

P

A

T

EPT

MT X W R

PTE:

4KB

page

S

V

E

Ignored

0 0 0

PTE:

not

present

Figure 28-1. Formats of EPTP and EPT Paging-Structure Entries

NOTES:

1. M is an abbreviation for MAXPHYADDR.

2. See Section 24.6.11 for details of the EPTP.

3. Suppress #VE. If the “EPT-violation #VE” VM-execution control is 0, this bit is ignored.