27-8 Vol. 3C

VM EXITS

Bit 12 is undefined in any of the following cases:

•

If the “NMI exiting” VM-execution control is 1 and the “virtual NMIs” VM-execution control is 0.

•

If the VM exit sets the valid bit in the IDT-vectoring information field (see Section 27.2.3).

Otherwise, bit 12 is defined as follows:

•

If the “virtual NMIs” VM-execution control is 0, the EPT violation was caused by a memory access as

part of execution of the IRET instruction, and blocking by NMI (see Table 24-3) was in effect before

execution of IRET, bit 12 is set to 1.

•

If the “virtual NMIs” VM-execution control is 1,the EPT violation was caused by a memory access as part

of execution of the IRET instruction, and virtual-NMI blocking was in effect before execution of IRET,

bit 12 is set to 1.

•

For all other relevant VM exits, bit 12 is cleared to 0.

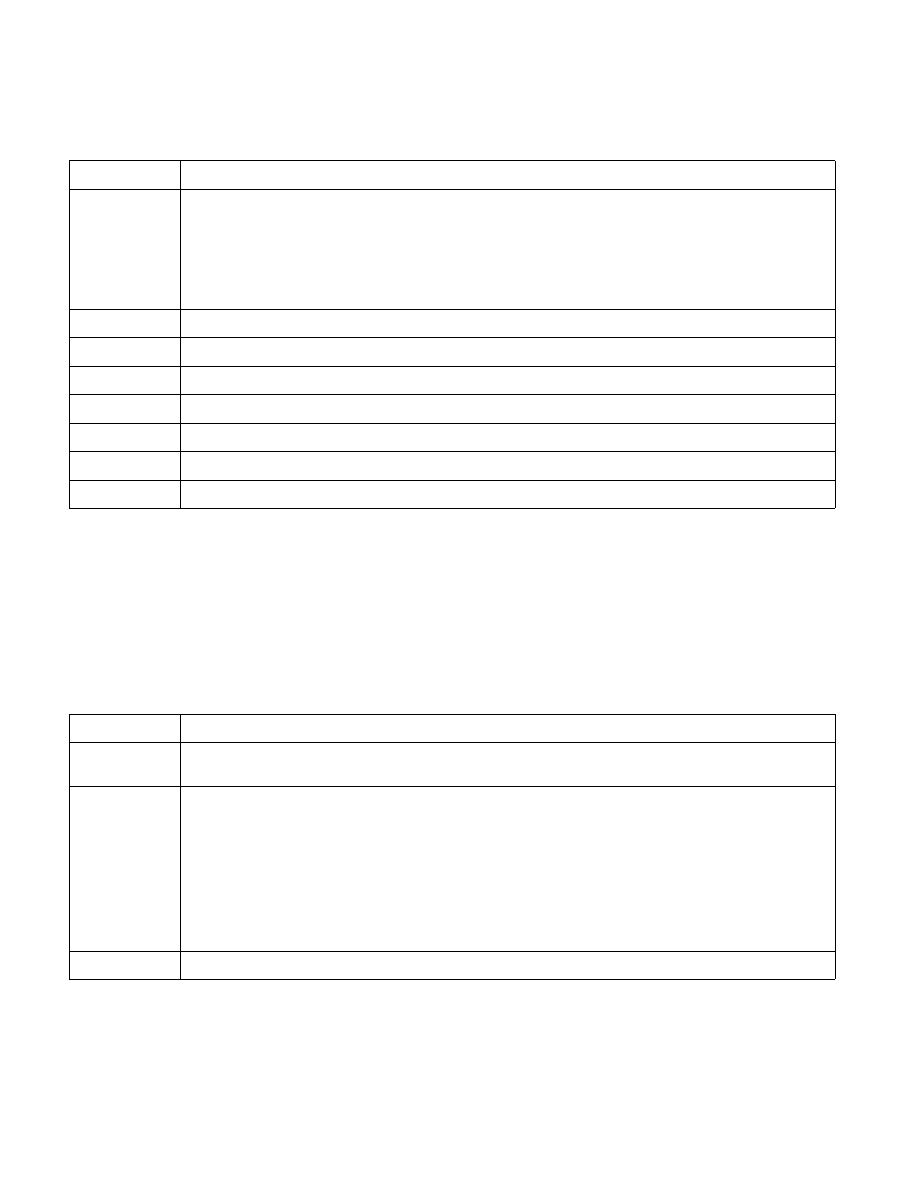

Table 27-5. Exit Qualification for I/O Instructions

Bit Position(s)

Contents

2:0

Size of access:

0 = 1-byte

1 = 2-byte

3 = 4-byte

Other values not used

3

Direction of the attempted access (0

=

OUT, 1

=

IN)

4

String instruction (0 = not string; 1 = string)

5

REP prefixed (0 = not REP; 1 = REP)

6

Operand encoding (0 = DX, 1 = immediate)

15:7

Reserved (cleared to 0)

31:16

Port number (as specified in DX or in an immediate operand)

63:32

Reserved (cleared to 0). These bits exist only on processors that support Intel 64 architecture.

Table 27-6. Exit Qualification for APIC-Access VM Exits from Linear Accesses and Guest-Physical Accesses

Bit Position(s)

Contents

11:0

• If the APIC-access VM exit is due to a linear access, the offset of access within the APIC page.

• Undefined if the APIC-access VM exit is due a guest-physical access

15:12

Access type:

0 = linear access for a data read during instruction execution

1 = linear access for a data write during instruction execution

2 = linear access for an instruction fetch

3 = linear access (read or write) during event delivery

10 = guest-physical access during event delivery

15 = guest-physical access for an instruction fetch or during instruction execution

Other values not used

63:16

Reserved (cleared to 0). Bits 63:32 exist only on processors that support Intel 64 architecture.