4-10 Vol. 3A

PAGING

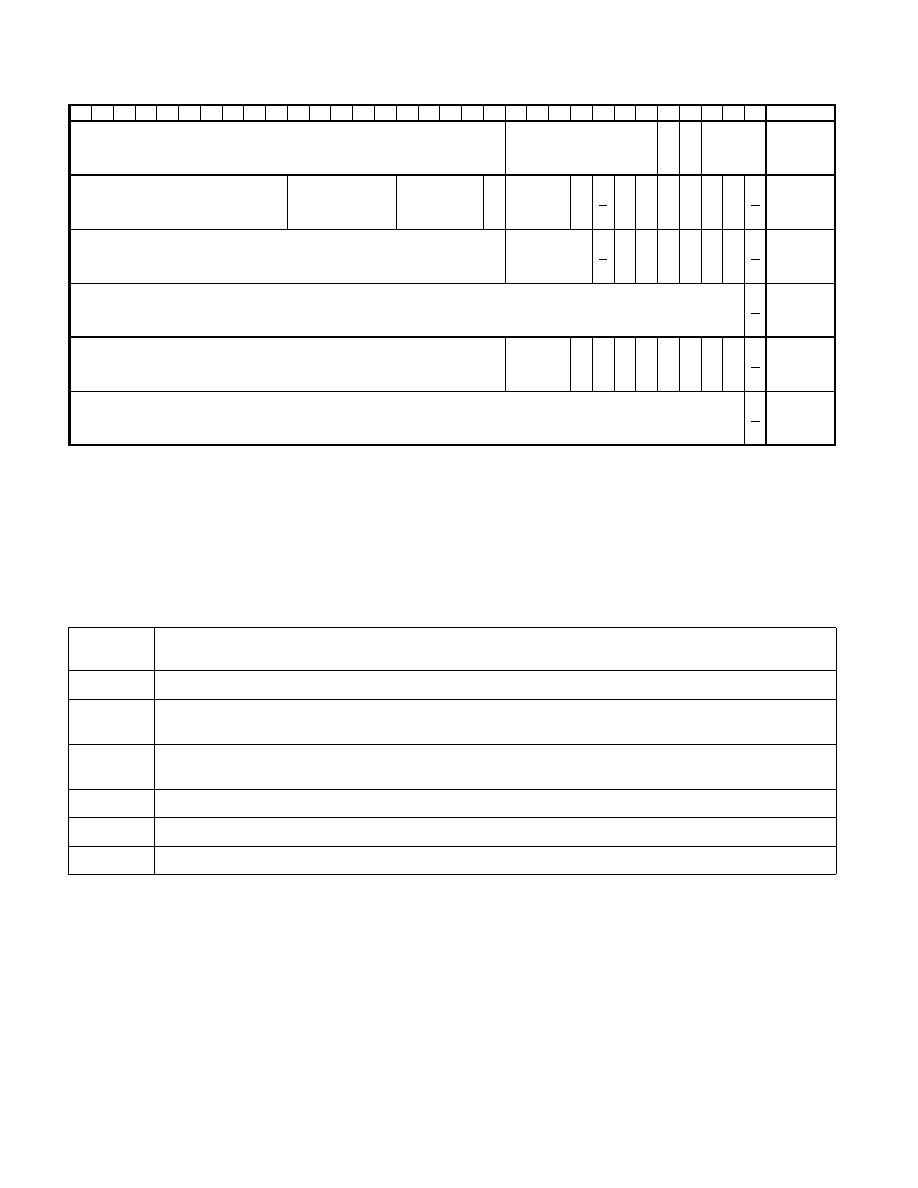

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Address of page directory

1

Ignored

P

C

D

PW

T

Ignored

CR3

Bits 31:22 of address

of 4MB page frame

Reserved

(must be 0)

Bits 39:32 of

address

2

P

A

T

Ignored

G 1 D A

P

C

D

PW

T

U

/

S

R

/

W

1

PDE:

4MB

page

Address of page table

Ignored

0

I

g

n

A

P

C

D

PW

T

U

/

S

R

/

W

1

PDE:

page

table

Ignored

0

PDE:

not

present

Address of 4KB page frame

Ignored

G

P

A

T

D A

P

C

D

PW

T

U

/

S

R

/

W

1

PTE:

4KB

page

Ignored

0

PTE:

not

present

Figure 4-4. Formats of CR3 and Paging-Structure Entries with 32-Bit Paging

NOTES:

1. CR3 has 64 bits on processors supporting the Intel-64 architecture. These bits are ignored with 32-bit paging.

2. This example illustrates a processor in which MAXPHYADDR is 36. If this value is larger or smaller, the number of bits reserved in

positions 20:13 of a PDE mapping a 4-MByte page will change.

Table 4-3. Use of CR3 with 32-Bit Paging

Bit

Position(s)

Contents

2:0

Ignored

3 (PWT)

Page-level write-through; indirectly determines the memory type used to access the page directory during linear-

address translation (see Section 4.9)

4 (PCD)

Page-level cache disable; indirectly determines the memory type used to access the page directory during linear-

address translation (see Section 4.9)

11:5

Ignored

31:12

Physical address of the 4-KByte aligned page directory used for linear-address translation

63:32

Ignored (these bits exist only on processors supporting the Intel-64 architecture)