Vol. 3C 24-17

VIRTUAL MACHINE CONTROL STRUCTURES

•

EPTP index (16 bits). When an EPT violation causes a virtualization exception, the processor writes the value

of this field to the virtualization-exception information area. The EPTP-switching VM function updates this field

(see Section 25.5.5.3).

24.6.19 XSS-Exiting

Bitmap

On processors that support the 1-setting of the “enable XSAVES/XRSTORS” VM-execution control, the VM-execu-

tion control fields include a 64-bit XSS-exiting bitmap. If the “enable XSAVES/XRSTORS” VM-execution control is

1, executions of XSAVES and XRSTORS may consult this bitmap (see Section 25.1.3 and Section 25.3).

24.7

VM-EXIT CONTROL FIELDS

The VM-exit control fields govern the behavior of VM exits. They are discussed in Section 24.7.1 and Section

24.7.2.

24.7.1 VM-Exit

Controls

The VM-exit controls constitute a 32-bit vector that governs the basic operation of VM exits. Table 24-10 lists the

controls supported. See Chapter 27 for complete details of how these controls affect VM exits.

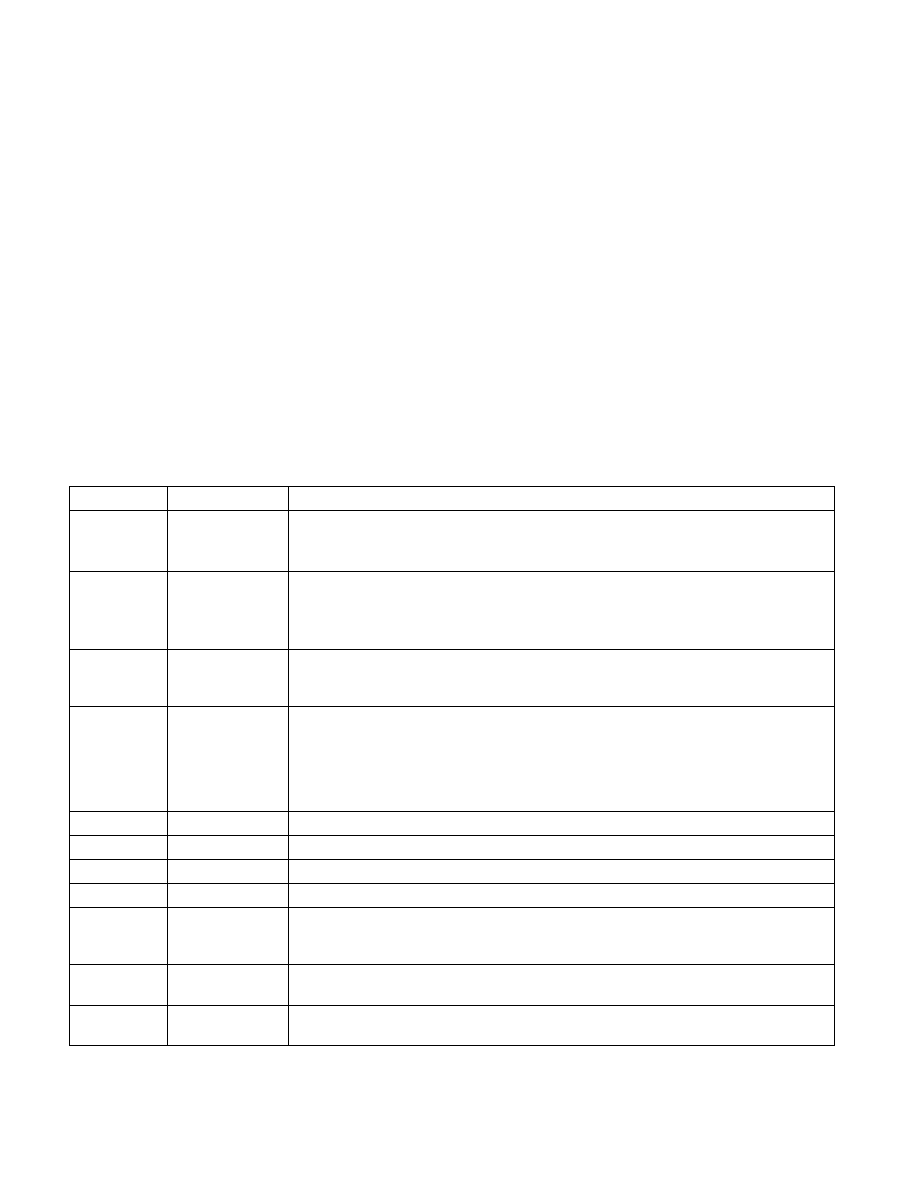

Table 24-10. Definitions of VM-Exit Controls

Bit Position(s) Name

Description

2

Save debug

controls

This control determines whether DR7 and the IA32_DEBUGCTL MSR are saved on VM exit.

The first processors to support the virtual-machine extensions supported only the 1-setting

of this control.

9

Host address-

space size

On processors that support Intel 64 architecture, this control determines whether a logical

processor is in 64-bit mode after the next VM exit. Its value is loaded into CS.L,

IA32_EFER.LME, and IA32_EFER.LMA on every VM exit.

1

This control must be 0 on processors that do not support Intel 64 architecture.

12

Load

IA32_PERF_GLOB

AL_CTRL

This control determines whether the IA32_PERF_GLOBAL_CTRL MSR is loaded on VM exit.

15

Acknowledge

interrupt on exit

This control affects VM exits due to external interrupts:

• If such a VM exit occurs and this control is 1, the logical processor acknowledges the

interrupt controller, acquiring the interrupt’s vector. The vector is stored in the VM-exit

interruption-information field, which is marked valid.

• If such a VM exit occurs and this control is 0, the interrupt is not acknowledged and the

VM-exit interruption-information field is marked invalid.

18

Save IA32_PAT

This control determines whether the IA32_PAT MSR is saved on VM exit.

19

Load IA32_PAT

This control determines whether the IA32_PAT MSR is loaded on VM exit.

20

Save IA32_EFER

This control determines whether the IA32_EFER MSR is saved on VM exit.

21

Load IA32_EFER

This control determines whether the IA32_EFER MSR is loaded on VM exit.

22

Save VMX-

preemption timer

value

This control determines whether the value of the VMX-preemption timer is saved on VM exit.

23

Clear

IA32_BNDCFGS

This control determines whether the IA32_BNDCFGS MSR is cleared on VM exit.

24

Conceal VM exits

from Intel PT

If this control is 1, Intel Processor Trace does not produce a paging information packet (PIP) on

a VM exit (see Chapter 36).