22-36 Vol. 3B

ARCHITECTURE COMPATIBILITY

See Chapter 15, “Machine-Check Architecture,” for more information on the machine-check exception and the

machine-check architecture.

22.37.5 Performance-Monitoring

Counters

The P6 family and Pentium processors provide two performance-monitoring counters for use in monitoring internal

hardware operations. The number of performance monitoring counters and associated programming interfaces

may be implementation specific for Pentium 4 processors, Pentium M processors. Later processors may have

implemented these as part of an architectural performance monitoring feature. The architectural and non-architec-

tural performance monitoring interfaces for different processor families are described in Chapter 18, “Performance

Monitoring,”. Chapter 19, “Performance Monitoring Events.” lists all the events that can be counted for architectural

performance monitoring events and non-architectural events. The counters are set up, started, and stopped using

two MSRs and the RDMSR and WRMSR instructions. For the P6 family processors, the current count for a particular

counter can be read using the new RDPMC instruction.

The performance-monitoring counters are useful for debugging programs, optimizing code, diagnosing system fail-

ures, or refining hardware designs. See Chapter 18, “Performance Monitoring,” for more information on these

counters.

22.38 TWO WAYS TO RUN INTEL 286 PROCESSOR TASKS

When porting 16-bit programs to run on 32-bit IA-32 processors, there are two approaches to consider:

•

Porting an entire 16-bit software system to a 32-bit processor, complete with the old operating system, loader,

and system builder. Here, all tasks will have 16-bit TSSs. The 32-bit processor is being used as if it were a faster

version of the 16-bit processor.

•

Porting selected 16-bit applications to run in a 32-bit processor environment with a 32-bit operating system,

loader, and system builder. Here, the TSSs used to represent 286 tasks should be changed to 32-bit TSSs. It is

possible to mix 16 and 32-bit TSSs, but the benefits are small and the problems are great. All tasks in a 32-bit

software system should have 32-bit TSSs. It is not necessary to change the 16-bit object modules themselves;

TSSs are usually constructed by the operating system, by the loader, or by the system builder. See Chapter 21,

“Mixing 16-Bit and 32-Bit Code,” for more detailed information about mixing 16-bit and 32-bit code.

Because the 32-bit processors use the contents of the reserved word of 16-bit segment descriptors, 16-bit

programs that place values in this word may not run correctly on the 32-bit processors.

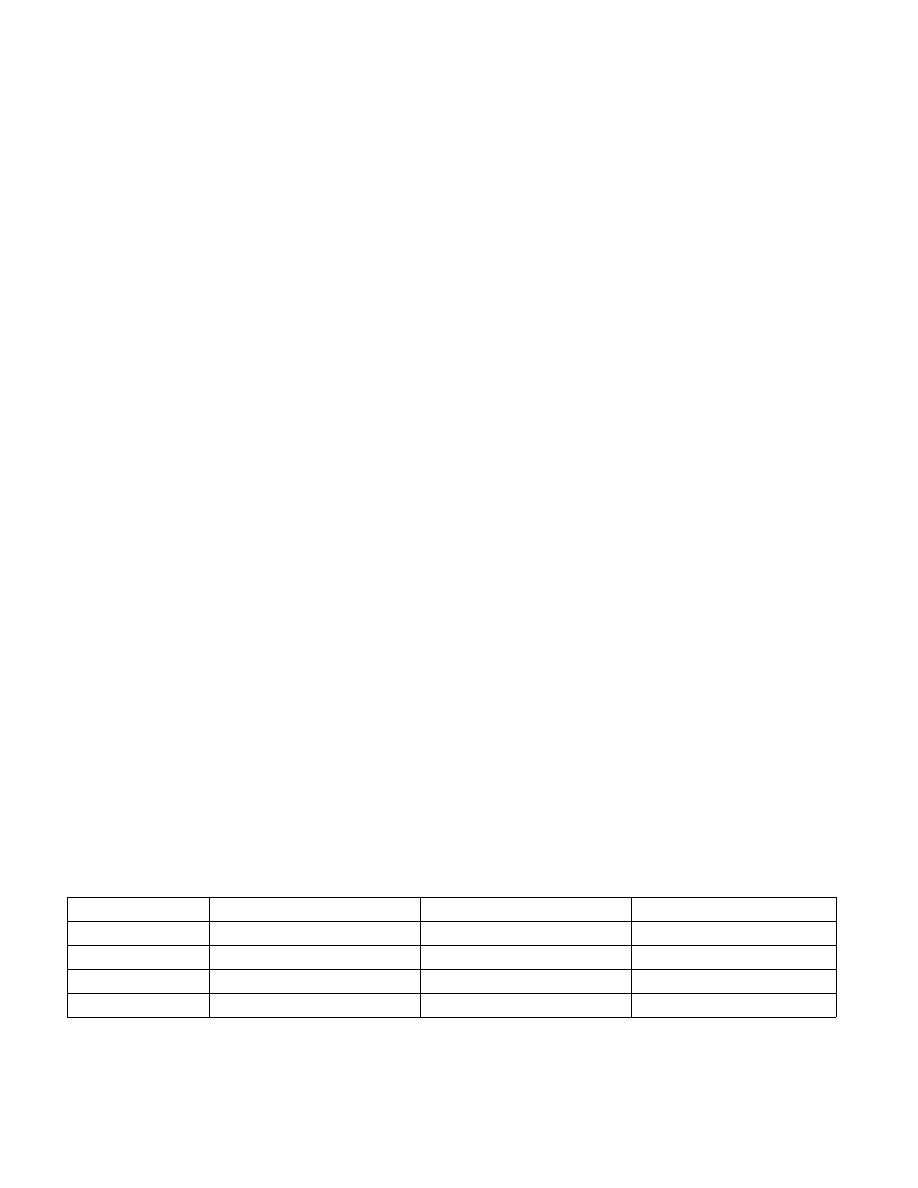

22.39 INITIAL STATE OF PENTIUM, PENTIUM PRO AND PENTIUM 4 PROCESSORS

Table 22-10 shows the state of the flags and other registers following power-up for the Pentium, Pentium Pro and

Pentium 4 processors. The state of control register CR0 is 60000010H (see Figure 9-1 “Contents of CR0 Register

after Reset” in the Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A). This places the

processor in real-address mode with paging disabled.

Table 22-10. Processor State Following Power-up/Reset/INIT for Pentium, Pentium Pro and Pentium 4 Processors

Register

Pentium 4 Processor

Pentium Pro Processor

Pentium Processor

EFLAGS

1

00000002H

00000002H

00000002H

EIP

0000FFF0H

0000FFF0H

0000FFF0H

CR0

60000010H

2

60000010H

2

60000010H

2

CR2, CR3, CR4

00000000H

00000000H

00000000H