22-16 Vol. 3B

ARCHITECTURE COMPATIBILITY

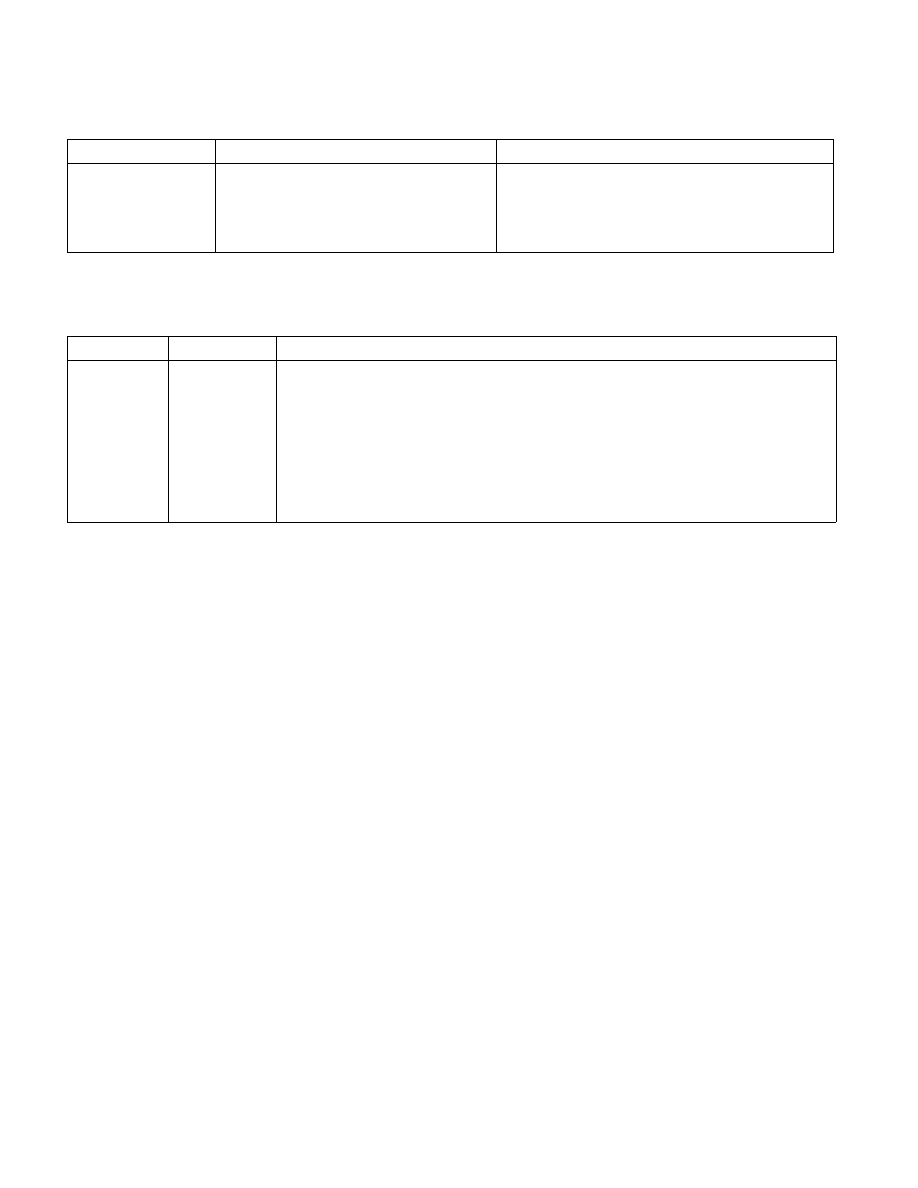

The EM and MP flags in register CR0 are interpreted as shown in Table 22-3.

Following is an example code sequence to initialize the system and check for the presence of Intel486 SX

processor/Intel 487 SX math coprocessor.

fninit

fstcw mem_loc

mov ax, mem_loc

cmp ax, 037fh

jz Intel487_SX_Math_CoProcessor_present

;ax=037fh

jmp Intel486_SX_microprocessor_present

;ax=ffffh

If the Intel 487 SX math coprocessor is not present, the following code can be run to set the CR0 register for the

Intel486 SX processor.

mov eax, cr0

and eax, fffffffdh ;make MP=0

or eax, 0024h

;make EM=1, NE=1

mov cr0, eax

This initialization will cause any floating-point instruction to generate a device not available exception (#NH), inter-

rupt 7. The software emulation will then take control to execute these instructions. This code is not required if an

Intel 487 SX math coprocessor is present in the system. In that case, the typical initialization routine for the

Intel486 SX microprocessor will be adequate.

Also, when designing an Intel486 SX processor based system with an Intel 487 SX math coprocessor, timing loops

should be independent of frequency and clocks per instruction. One way to attain this is to implement these loops

in hardware and not in software (for example, BIOS).

22.21 CONTROL

REGISTERS

The following sections identify the new control registers and control register flags and fields that were introduced

to the 32-bit IA-32 in various processor families. See Figure 2-7 for the location of these flags and fields in the

control registers.

Table 22-2. Recommended Values of the EM, MP, and NE Flags for Intel486 SX Microprocessor/Intel 487 SX Math

Coprocessor System

CR0 Flags

Intel486 SX Processor Only

Intel 487 SX Math Coprocessor Present

EM

1

0

MP

0

1

NE

1

0, for MS-DOS* systems

1, for user-defined exception handler

Table 22-3. EM and MP Flag Interpretation

EM

MP

Interpretation

0

0

Floating-point instructions are passed to FPU; WAIT/FWAIT and other waiting-type instructions

ignore TS.

0

1

Floating-point instructions are passed to FPU; WAIT/FWAIT and other waiting-type instructions

test TS.

1

0

Floating-point instructions trap to emulator; WAIT/FWAIT and other waiting-type instructions

ignore TS.

1

1

Floating-point instructions trap to emulator; WAIT/FWAIT and other waiting-type instructions

test TS.