22-4 Vol. 3B

ARCHITECTURE COMPATIBILITY

22.11 MULTI-CORE

TECHNOLOGY

The Pentium D processor and Pentium processor Extreme Edition provide two processor cores in each physical

processor package. See also: Section 8.5, “Intel

Hyper-Threading Technology and Intel

and Section 8.8, “Multi-Core Architecture.” Intel Core 2 Duo, Intel Pentium Dual-Core processors, Intel Xeon

processors 3000, 3100, 5100, 5200 series provide two processor cores in each physical processor package. Intel

Core 2 Extreme, Intel Core 2 Quad processors, Intel Xeon processors 3200, 3300, 5300, 5400, 7300 series provide

two processor cores in each physical processor package.

22.12 SPECIFIC FEATURES OF DUAL-CORE PROCESSOR

Dual-core processors may have some processor-specific features. Use CPUID feature flags to detect the availability

features. Note the following:

•

CPUID Brand String — On Pentium processor Extreme Edition, the process will report the correct brand string

only after the correct microcode updates are loaded.

•

Enhanced Intel SpeedStep Technology — This feature is supported in Pentium D processor but not in

Pentium processor Extreme Edition.

22.13 NEW INSTRUCTIONS IN THE PENTIUM AND LATER IA-32 PROCESSORS

Table 22-1 identifies the instructions introduced into the IA-32 in the Pentium processor and later IA-32 processors.

22.13.1 Instructions Added Prior to the Pentium Processor

The following instructions were added in the Intel486 processor:

•

BSWAP (byte swap) instruction.

•

XADD (exchange and add) instruction.

•

CMPXCHG (compare and exchange) instruction.

•

ΙNVD (invalidate cache) instruction.

•

WBINVD (write-back and invalidate cache) instruction.

•

INVLPG (invalidate TLB entry) instruction.

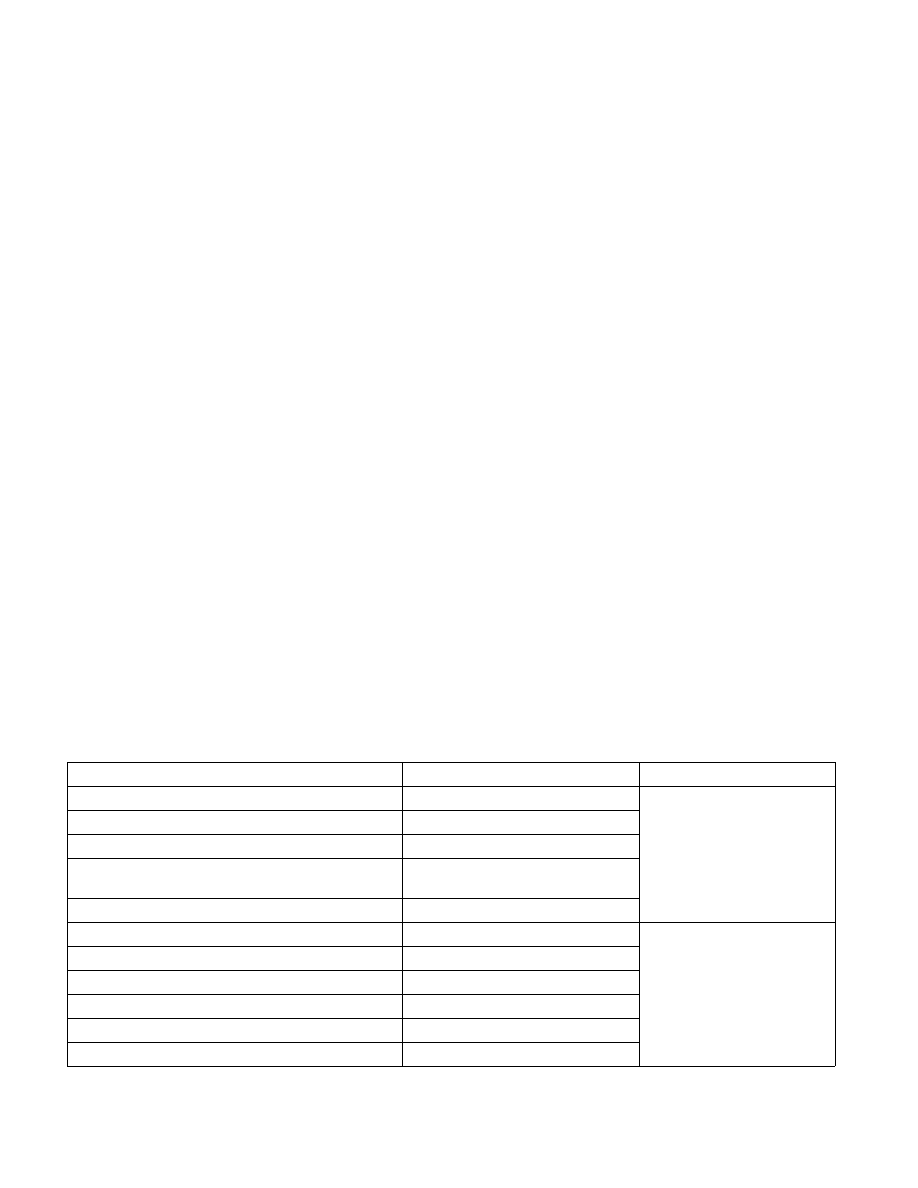

Table 22-1. New Instruction in the Pentium Processor and Later IA-32 Processors

Instruction

CPUID Identification Bits

Introduced In

CMOVcc (conditional move)

EDX, Bit 15

Pentium Pro processor

FCMOVcc (floating-point conditional move)

EDX, Bits 0 and 15

FCOMI (floating-point compare and set EFLAGS)

EDX, Bits 0 and 15

RDPMC (read performance monitoring counters)

EAX, Bits 8-11, set to 6H;

see Note 1

UD2 (undefined)

EAX, Bits 8-11, set to 6H

CMPXCHG8B (compare and exchange 8 bytes)

EDX, Bit 8

Pentium processor

CPUID (CPU identification)

None; see Note 2

RDTSC (read time-stamp counter)

EDX, Bit 4

RDMSR (read model-specific register)

EDX, Bit 5

WRMSR (write model-specific register)

EDX, Bit 5

MMX Instructions

EDX, Bit 23