CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

3-190 Vol. 2A

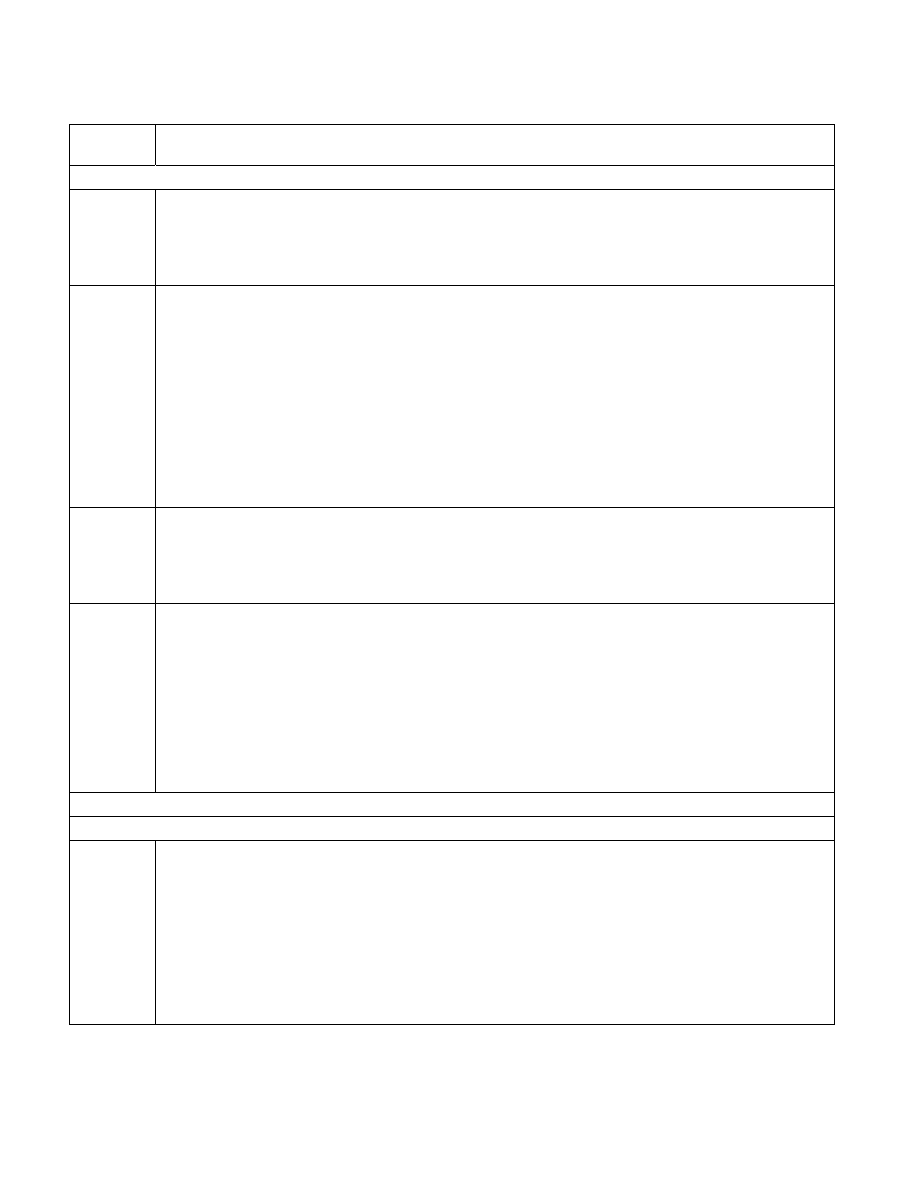

Table 3-8. Information Returned by CPUID Instruction

Initial EAX

Value

Information Provided about the Processor

Basic CPUID Information

0H

EAX

Maximum Input Value for Basic CPUID Information.

EBX

“Genu”

ECX

“ntel”

EDX

“ineI”

01H

EAX

Version Information: Type, Family, Model, and Stepping ID (see Figure 3-6).

EBX

Bits 07 - 00: Brand Index.

Bits 15 - 08: CLFLUSH line size (Value ∗ 8 = cache line size in bytes; used also by CLFLUSHOPT).

Bits 23 - 16: Maximum number of addressable IDs for logical processors in this physical package*.

Bits 31 - 24: Initial APIC ID.

ECX

Feature Information (see Figure 3-7 and Table 3-10).

EDX

Feature Information (see Figure 3-8 and Table 3-11).

NOTES:

* The nearest power-of-2 integer that is not smaller than EBX[23:16] is the number of unique initial APIC

IDs reserved for addressing different logical processors in a physical package. This field is only valid if

CPUID.1.EDX.HTT[bit 28]= 1.

02H

EAX

Cache and TLB Information (see Table 3-12).

EBX

Cache and TLB Information.

ECX

Cache and TLB Information.

EDX

Cache and TLB Information.

03H

EAX

Reserved.

EBX

Reserved.

ECX

Bits 00 - 31 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the

value in this register is reserved.)

EDX

Bits 32 - 63 of 96 bit processor serial number. (Available in Pentium III processor only; otherwise, the

value in this register is reserved.)

NOTES:

Processor serial number (PSN) is not supported in the Pentium 4 processor or later. On all models, use

the PSN flag (returned using CPUID) to check for PSN support before accessing the feature.

CPUID leaves above 2 and below 80000000H are visible only when IA32_MISC_ENABLE[bit 22] has its default value of 0.

Deterministic Cache Parameters Leaf

04H

NOTES:

Leaf 04H output depends on the initial value in ECX.*

See also: “INPUT EAX = 04H: Returns Deterministic Cache Parameters for Each Level” on page 213.

EAX

Bits 04 - 00: Cache Type Field.

0 = Null - No more caches.

1 = Data Cache.

2 = Instruction Cache.

3 = Unified Cache.

4-31 = Reserved.