CPUID—CPU Identification

INSTRUCTION SET REFERENCE, A-L

3-208 Vol. 2A

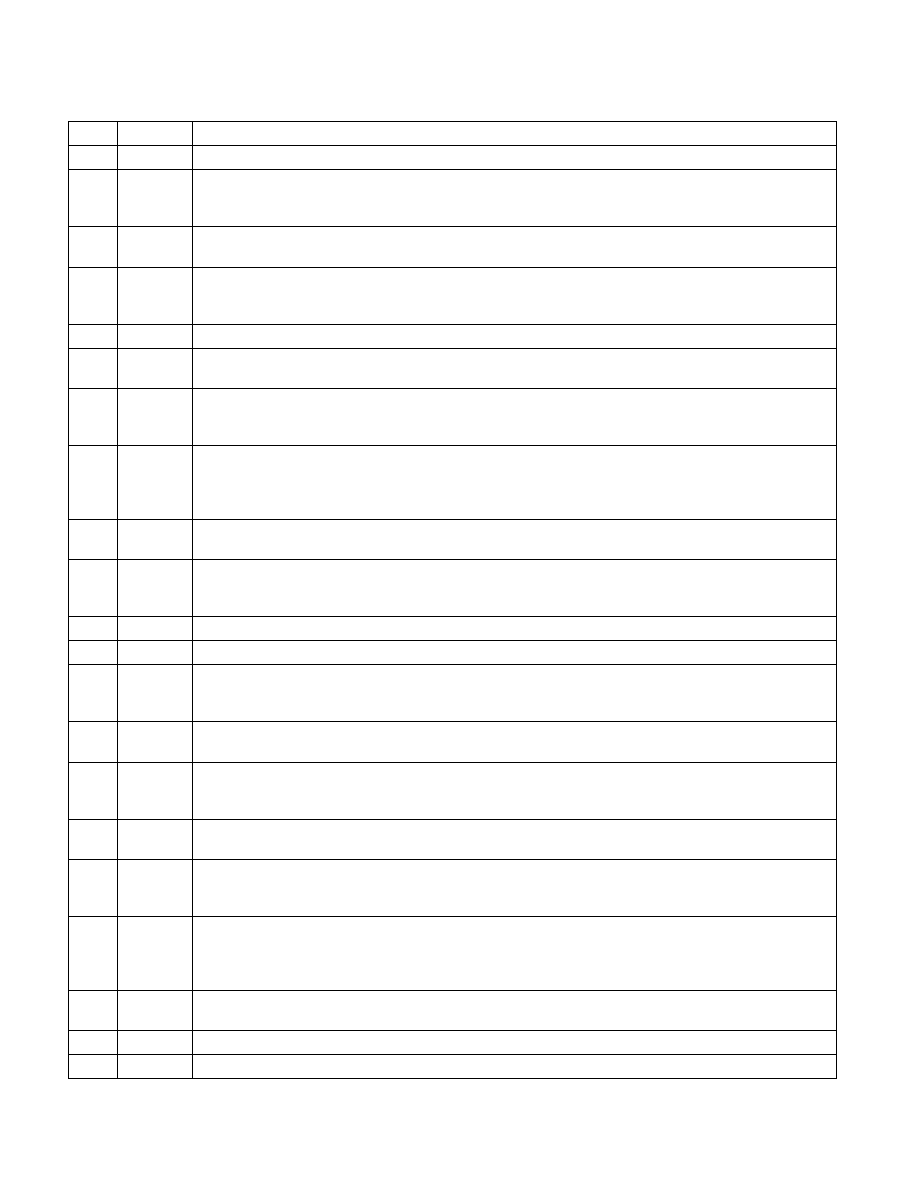

Table 3-11. More on Feature Information Returned in the EDX Register

Bit # Mnemonic Description

0 FPU

Floating Point Unit On-Chip. The processor contains an x87 FPU.

1 VME

Virtual 8086 Mode Enhancements. Virtual 8086 mode enhancements, including CR4.VME for controlling the

feature, CR4.PVI for protected mode virtual interrupts, software interrupt indirection, expansion of the TSS

with the software indirection bitmap, and EFLAGS.VIF and EFLAGS.VIP flags.

2 DE

Debugging Extensions. Support for I/O breakpoints, including CR4.DE for controlling the feature, and optional

trapping of accesses to DR4 and DR5.

3 PSE

Page Size Extension. Large pages of size 4 MByte are supported, including CR4.PSE for controlling the

feature, the defined dirty bit in PDE (Page Directory Entries), optional reserved bit trapping in CR3, PDEs, and

PTEs.

4 TSC

Time Stamp Counter. The RDTSC instruction is supported, including CR4.TSD for controlling privilege.

5 MSR

Model Specific Registers RDMSR and WRMSR Instructions. The RDMSR and WRMSR instructions are

supported. Some of the MSRs are implementation dependent.

6 PAE

Physical Address Extension.

Physical addresses greater than 32 bits are supported: extended page table

entry formats, an extra level in the page translation tables is defined, 2-MByte pages are supported instead of

4 Mbyte pages if PAE bit is 1.

7 MCE

Machine Check Exception. Exception 18 is defined for Machine Checks, including CR4.MCE for controlling the

feature. This feature does not define the model-specific implementations of machine-check error logging,

reporting, and processor shutdowns. Machine Check exception handlers may have to depend on processor

version to do model specific processing of the exception, or test for the presence of the Machine Check feature.

8 CX8

CMPXCHG8B Instruction. The compare-and-exchange 8 bytes (64 bits) instruction is supported (implicitly

locked and atomic).

9 APIC

APIC On-Chip. The processor contains an Advanced Programmable Interrupt Controller (APIC), responding to

memory mapped commands in the physical address range FFFE0000H to FFFE0FFFH (by default - some

processors permit the APIC to be relocated).

10 Reserved Reserved

11

SEP

SYSENTER and SYSEXIT Instructions. The SYSENTER and SYSEXIT and associated MSRs are supported.

12 MTRR

Memory Type Range Registers. MTRRs are supported. The MTRRcap MSR contains feature bits that describe

what memory types are supported, how many variable MTRRs are supported, and whether fixed MTRRs are

supported.

13 PGE

Page Global Bit. The global bit is supported in paging-structure entries that map a page, indicating TLB entries

that are common to different processes and need not be flushed. The CR4.PGE bit controls this feature.

14 MCA

Machine Check Architecture. A value of 1 indicates the Machine Check Architecture of reporting machine

errors is supported. The MCG_CAP MSR contains feature bits describing how many banks of error reporting

MSRs are supported.

15 CMOV

Conditional Move Instructions. The conditional move instruction CMOV is supported. In addition, if x87 FPU is

present as indicated by the CPUID.FPU feature bit, then the FCOMI and FCMOV instructions are supported

16 PAT

Page Attribute Table. Page Attribute Table is supported. This feature augments the Memory Type Range

Registers (MTRRs), allowing an operating system to specify attributes of memory accessed through a linear

address on a 4KB granularity.

17 PSE-36 36-Bit Page Size Extension. 4-MByte pages addressing physical memory beyond 4 GBytes are supported with

32-bit paging. This feature indicates that upper bits of the physical address of a 4-MByte page are encoded in

bits 20:13 of the page-directory entry. Such physical addresses are limited by MAXPHYADDR and may be up to

40 bits in size.

18 PSN

Processor Serial Number. The processor supports the 96-bit processor identification number feature and the

feature is enabled.

19 CLFSH

CLFLUSH Instruction. CLFLUSH Instruction is supported.

20

Reserved Reserved