D-4 Vol. 1

GUIDELINES FOR WRITING X87 FPU EXCEPTION HANDLERS

D.2.1.2

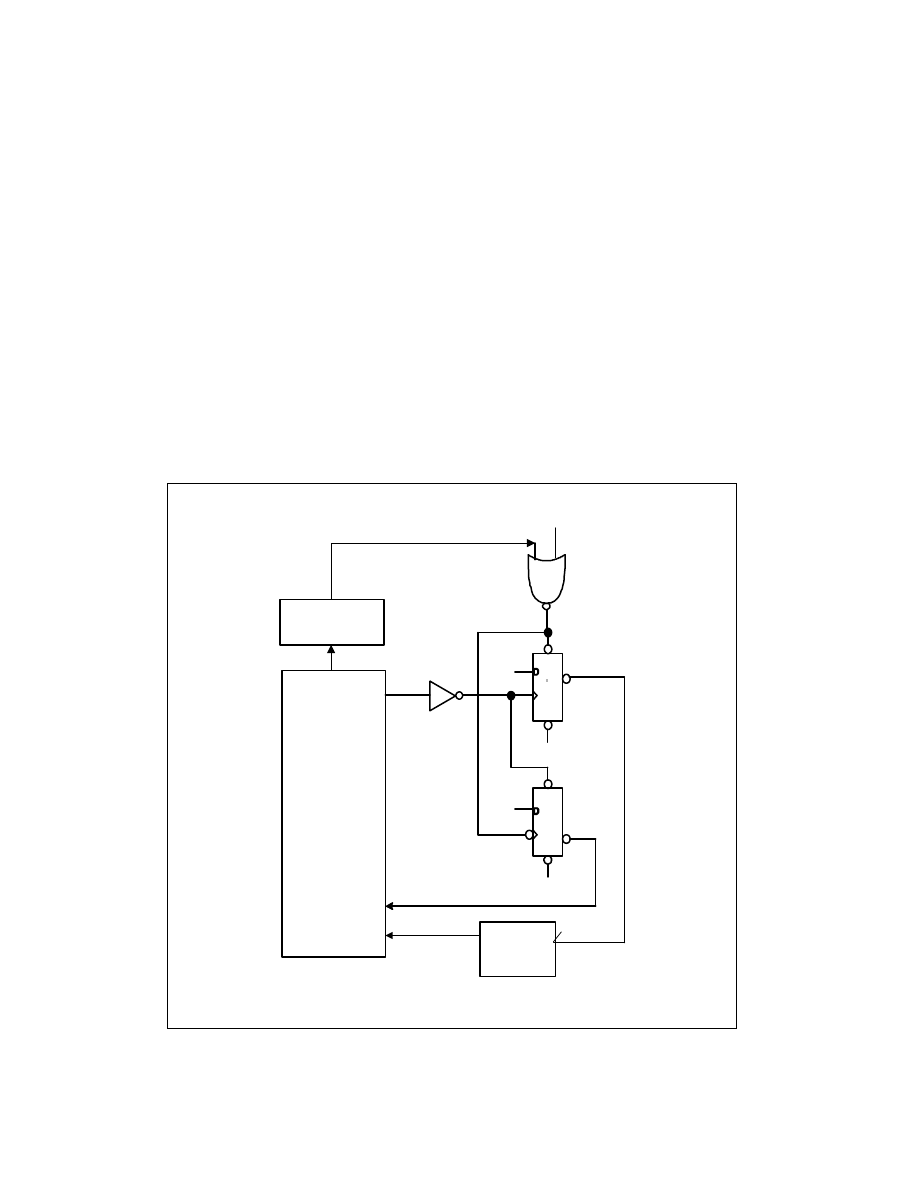

Recommended External Hardware to Support the MS-DOS* Compatibility Sub-mode

Figure D-1 provides an external circuit that will assure proper handling of FERR# and IGNNE# when an x87 FPU

exception occurs. In particular, it assures that IGNNE# will be active only inside the x87 FPU exception handler

without depending on the order of actions by the exception handler. Some hardware implementations have been

less robust because they have depended on the exception handler to clear the x87 FPU exception interrupt request

to the PIC (FP_IRQ signal) before the handler causes FERR# to be de-asserted by clearing the exception from the

x87 FPU itself. Figure D-2 shows the details of how IGNNE# will behave when the circuit in Figure D-1 is imple-

mented. The temporal regions within the x87 FPU exception handler activity are described as follows:

1. The FERR# signal is activated by an x87 FPU exception and sends an interrupt request through the PIC to the

processor’s INTR pin.

2. During the x87 FPU interrupt service routine (exception handler) the processor will need to clear the interrupt

request latch (Flip Flop #1). It may also want to execute non-control x87 FPU instructions before the exception

is cleared from the x87 FPU. For this purpose the IGNNE# must be driven low. Typically in the PC environment

an I/O access to Port 0F0H clears the external x87 FPU exception interrupt request (FP_IRQ). In the

recommended circuit, this access also is used to activate IGNNE#. With IGNNE# active, the x87 FPU exception

handler may execute any x87 FPU instruction without being blocked by an active x87 FPU exception.

3. Clearing the exception within the x87 FPU will cause the FERR# signal to be deactivated and then there is no

further need for IGNNE# to be active. In the recommended circuit, the deactivation of FERR# is used to

deactivate IGNNE#. If another circuit is used, the software and circuit together must assure that IGNNE# is

deactivated no later than the exit from the x87 FPU exception handler.

Figure D-1. Recommended Circuit for MS-DOS Compatibility x87 FPU

Exception Handling

I/O Port F0H

Address Decode

FERR#

IGNNE#

INTR

Interrupt

Controller

RESET

FP_IRQ

+5V

PR

+5V

+5V

+5V

PR

CLR

FF #1

FF #2

Intel486

™

Processor

Pentium

®

Processor

Pentium

®

Pro Processor

LEGEND:

FF #n Flip Flop #n

CLR Clear or Reset