Vol. 1 18-5

INPUT/OUTPUT

bit-map base address, the map has 11 bytes and the first 80 I/O ports are mapped. Higher addresses in the I/O

address space generate exceptions.

If the I/O bit map base address is greater than or equal to the TSS segment limit, there is no I/O permission map,

and all I/O instructions generate exceptions when the CPL is greater than the current IOPL.

18.6 ORDERING

I/O

When controlling I/O devices it is often important that memory and I/O operations be carried out in precisely the

order programmed. For example, a program may write a command to an I/O port, then read the status of the I/O

device from another I/O port. It is important that the status returned be the status of the device after it receives

the command, not before.

When using memory-mapped I/O, caution should be taken to avoid situations in which the programmed order is

not preserved by the processor. To optimize performance, the processor allows cacheable memory reads to be

reordered ahead of buffered writes in most situations. Internally, processor reads (cache hits) can be reordered

around buffered writes. When using memory-mapped I/O, therefore, it is possible that an I/O read might be

performed before the memory write of a previous instruction. The recommended method of enforcing program

ordering of memory-mapped I/O accesses with the Pentium 4, Intel Xeon, and P6 family processors is to use the

MTRRs to make the memory mapped I/O address space uncacheable; for the Pentium and Intel486 processors,

either the KEN# pin or the PCD flags can be used for this purpose (see Section 18.3.1, ÔÇťMemory-Mapped I/OÔÇŁ).

When the target of a read or write is in an uncacheable region of memory, memory reordering does not occur

externally at the processorÔÇÖs pins (that is, reads and writes appear in-order). Designating a memory mapped I/O

region of the address space as uncacheable insures that reads and writes of I/O devices are carried out in program

order. See Chapter 11, ÔÇťMemory Cache ControlÔÇŁ in the Intel┬« 64 and IA-32 Architectures Software DeveloperÔÇÖs

Manual, Volume 3A, for more information on using MTRRs.

Another method of enforcing program order is to insert one of the serializing instructions, such as the CPUID

instruction, between operations. See Chapter 8, ÔÇťMultiple-Processor ManagementÔÇŁ in the Intel┬« 64 and IA-32

Architectures Software DeveloperÔÇÖs Manual, Volume 3A, for more information on serialization of instructions.

It should be noted that the chip set being used to support the processor (bus controller, memory controller, and/or

I/O controller) may post writes to uncacheable memory which can lead to out-of-order execution of memory

accesses. In situations where out-of-order processing of memory accesses by the chip set can potentially cause

faulty memory-mapped I/O processing, code must be written to force synchronization and ordering of I/O opera-

tions. Serializing instructions can often be used for this purpose.

When the I/O address space is used instead of memory-mapped I/O, the situation is different in two respects:

ÔÇó

The processor never buffers I/O writes. Therefore, strict ordering of I/O operations is enforced by the

processor. (As with memory-mapped I/O, it is possible for a chip set to post writes in certain I/O ranges.)

ÔÇó

The processor synchronizes I/O instruction execution with external bus activity (see Table 18-1).

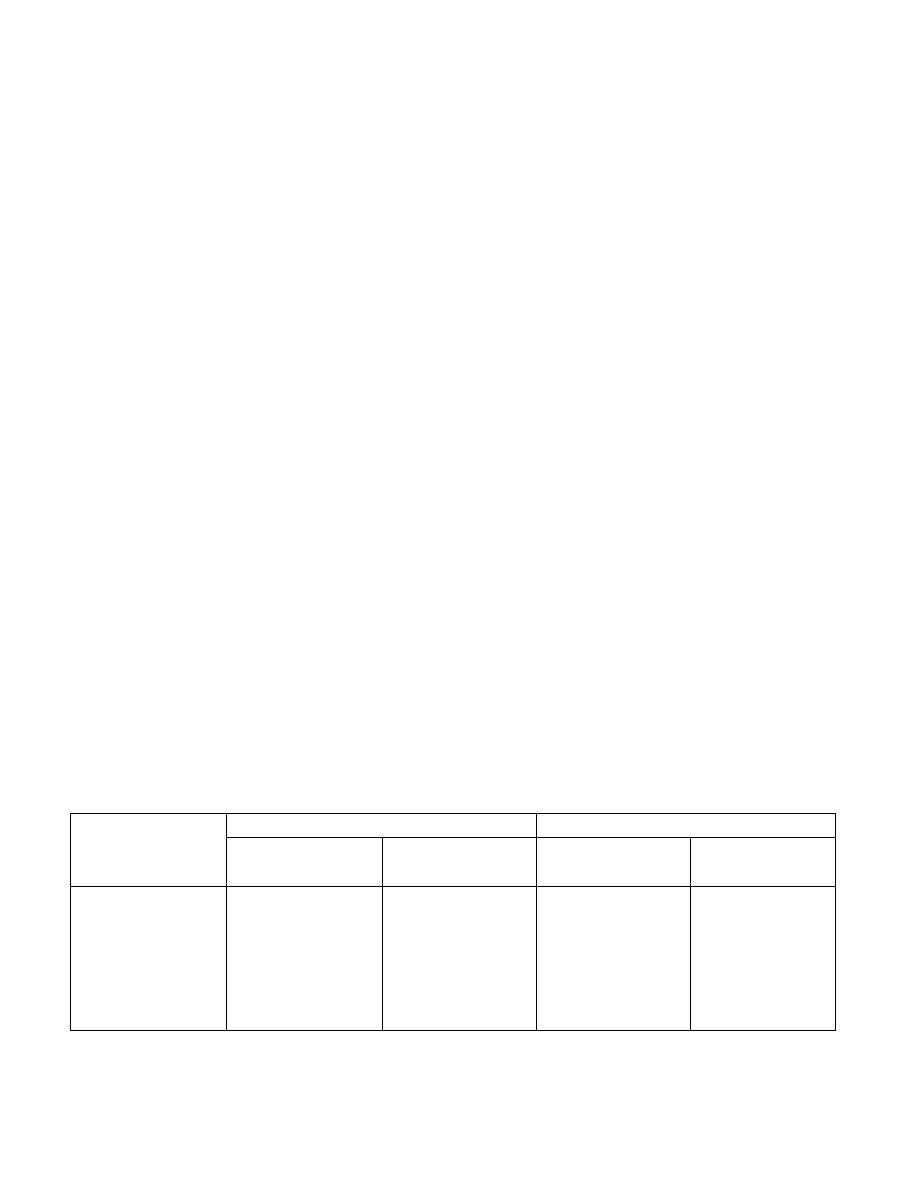

Table 18-1. I/O Instruction Serialization

Instruction Being

Executed

Processor Delays Execution of ÔÇŽ

Until Completion of ÔÇŽ

Current Instruction?

Next Instruction?

Pending Stores?

Current Store?

IN

Yes

Yes

INS

Yes

Yes

REP INS

Yes

Yes

OUT

Yes

Yes

Yes

OUTS

Yes

Yes

Yes

REP OUTS

Yes

Yes

Yes