Vol. 1 10-15

PROGRAMMING WITH INTEL® STREAMING SIMD EXTENSIONS (INTEL® SSE)

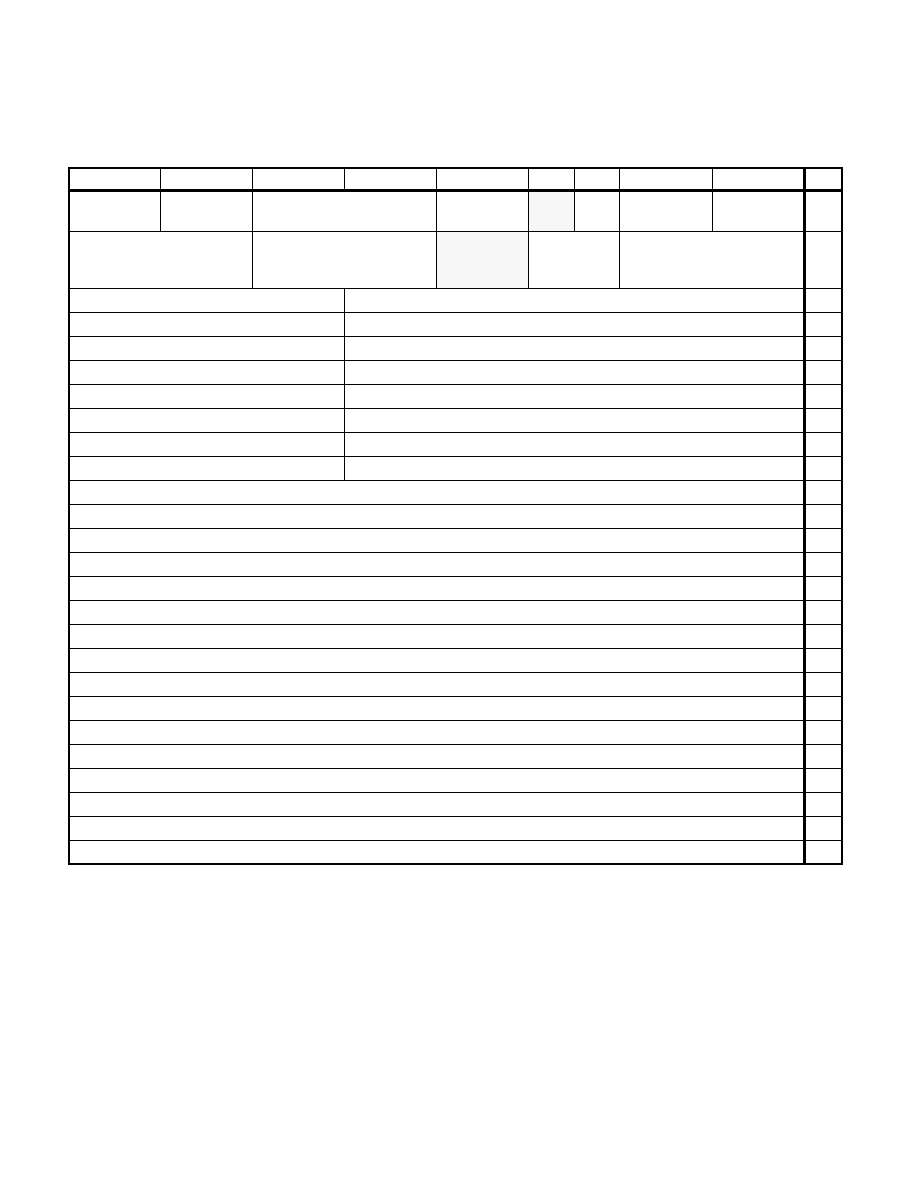

Every FXSAVE area comprises the 512 bytes starting at the area’s base address. Table 10-2 illustrates the format

of the first 416 bytes of the legacy region of an FXSAVE area.

The x87 state component comprises bytes 23:0 and bytes 159:32. The SSE state component comprises

bytes 31:24 and bytes 415:160. FXSAVE and FXRSTOR do not use bytes 511:416; bytes 463:416 are reserved.

Section 10.5.2 and Section 10.5.3 provide details of how FXSAVE and FXRSTOR use an FXSAVE area.

10.5.1.1 x87 State

Table 10-2 illustrates how FXSAVE and FXRSTOR organize x87 state and SSE state; the x87 state is listed below,

along with details of its interactions with FXSAVE and FXRSTOR:

•

Bytes 1:0, 3:2, and 7:6 are used for x87 FPU Control Word (FCW), x87 FPU Status Word (FSW), and x87 FPU

Opcode (FOP), respectively.

Table 10-2. Format of an FXSAVE Area

15 14

13 12

11 10

9

8

7

6

5

4

3

2

1

0

Reserved

CS or FPU

IP bits 63:32

FPU IP bits 31:0

FOP

Rsvd. FTW

FSW

FCW

0

MXCSR_MASK

MXCSR

Reserved

DS or

FPU DP

bits 63:32

FPU DP bits 31:0

16

Reserved

ST0/MM0

32

Reserved

ST1/MM1

48

Reserved

ST2/MM2

64

Reserved

ST3/MM3

80

Reserved

ST4/MM4

96

Reserved

ST5/MM5

112

Reserved

ST6/MM6

128

Reserved

ST7/MM7

144

XMM0

160

XMM1

176

XMM2

192

XMM3

208

XMM4

224

XMM5

240

XMM6

256

XMM7

272

XMM8

288

XMM9

304

XMM10

320

XMM11

336

XMM12

352

XMM13

368

XMM14

384

XMM15

400