8-14 Vol. 1

PROGRAMMING WITH THE X87 FPU

8.2.1 Indefinites

For each x87 FPU data type, one unique encoding is reserved for representing the special value indefinite. The x87

FPU produces indefinite values as responses to some masked floating-point invalid-operation exceptions. See

Tables 4-1, 4-3, and 4-4 for the encoding of the integer indefinite, QNaN floating-point indefinite, and packed BCD

integer indefinite, respectively.

The binary integer encoding 100..00B represents either of two things, depending on the circumstances of its use:

•

The largest negative number supported by the format (–2

15

, –2

31

, or –2

63

)

•

The integer indefinite value

If this encoding is used as a source operand (as in an integer load or integer arithmetic instruction), the x87 FPU

interprets it as the largest negative number representable in the format being used. If the x87 FPU detects an

invalid operation when storing an integer value in memory with an FIST/FISTP instruction and the invalid-operation

exception is masked, the x87 FPU stores the integer indefinite encoding in the destination operand as a masked

response to the exception. In situations where the origin of a value with this encoding may be ambiguous, the

invalid-operation exception flag can be examined to see if the value was produced as a response to an exception.

8.2.2 Unsupported

Double Extended-Precision

Floating-Point Encodings and Pseudo-Denormals

The double extended-precision floating-point format permits many encodings that do not fall into any of the cate-

gories shown in Table 4-3. Table 8-3 shows these unsupported encodings. Some of these encodings were supported

by the Intel 287 math coprocessor; however, most of them are not supported by the Intel 387 math coprocessor

and later IA-32 processors. These encodings are no longer supported due to changes made in the final version of

IEEE Standard 754 that eliminated these encodings.

Specifically, the categories of encodings formerly known as pseudo-NaNs, pseudo-infinities, and un-normal

numbers are not supported and should not be used as operand values. The Intel 387 math coprocessor and later

IA-32 processors generate an invalid-operation exception when these encodings are encountered as operands.

Beginning with the Intel 387 math coprocessor, the encodings formerly known as pseudo-denormal numbers are

not generated by IA-32 processors. When encountered as operands, however, they are handled correctly; that is,

they are treated as denormals and a denormal exception is generated. Pseudo-denormal numbers should not be

used as operand values. They are supported by current IA-32 processors (as described here) to support legacy

code.

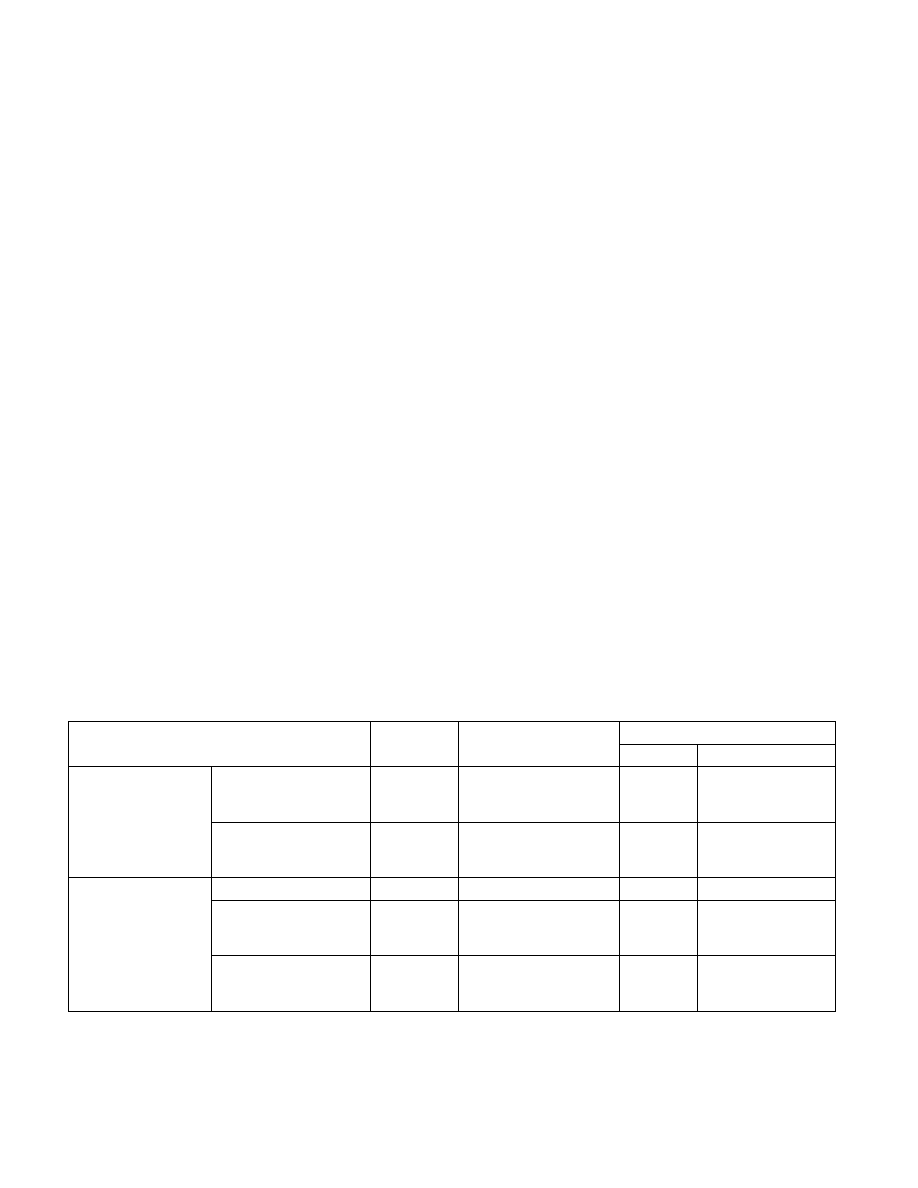

Table 8-3. Unsupported Double Extended-Precision Floating-Point Encodings and Pseudo-Denormals

Class

Sign

Biased Exponent

Significand

Integer

Fraction

Positive

Pseudo-NaNs

Quiet

0

.

0

11..11

.

11..11

0

11..11

.

10..00

Signaling

0

.

0

11..11

.

11..11

0

01..11

.

00..01

Positive Floating Point Pseudo-infinity

0

11..11

0

00..00

Unnormals

0

.

0

11..10

.

00..01

0

11..11

.

00..00

Pseudo-denormals

0

.

0

00..00

.

00..00

1

11..11

.

00..00