20-18 Vol. 3B

8086 EMULATION

Redirecting software interrupts back to the 8086 program potentially speeds up interrupt handling because a

switch back and forth between virtual-8086 mode and protected mode is not required. This latter interrupt-

handling technique is particularly useful for 8086 operating systems (such as MS-DOS) that use the INT n instruc-

tion to call operating system procedures.

The CPUID instruction can be used to verify that the virtual mode extension is implemented on the processor. Bit 1

of the feature flags register (EDX) indicates the availability of the virtual mode extension (see “CPUID—CPU Iden-

tification” in Chapter 3, “Instruction Set Reference, A-L”, of the Intel® 64 and IA-32 Architectures Software Devel-

oper’s Manual, Volume 2A).

The following sections describe the six methods (or mechanisms) for handling software interrupts in virtual-8086

mode. See Section 20.3.2, “Class 2—Maskable Hardware Interrupt Handling in Virtual-8086 Mode Using the Virtual

Interrupt Mechanism”, for a description of the use of the VIF and VIP flags in the EFLAGS register for handling

maskable hardware interrupts.

20.3.3.1 Method 1: Software Interrupt Handling

When the VME flag in control register CR4 is clear and the IOPL field is 3, a Pentium or later IA-32 processor

handles software interrupts in the same manner as they are handled by an Intel386 or Intel486 processor. It

executes an implicit call to the interrupt handler in the protected-mode IDT pointed to by the interrupt vector. See

Section 20.3.1, “Class 1—Hardware Interrupt and Exception Handling in Virtual-8086 Mode”, for a complete

description of this mechanism and its possible uses.

20.3.3.2 Methods 2 and 3: Software Interrupt Handling

When a software interrupt occurs in virtual-8086 mode and the method 2 or 3 conditions are present, the processor

generates a general-protection exception (#GP). Method 2 is enabled when the VME flag is set to 0 and the IOPL

value is less than 3. Here the IOPL value is used to bypass the protected-mode interrupt handlers and cause any

software interrupt that occurs in virtual-8086 mode to be treated as a protected-mode general-protection excep-

tion (#GP). The general-protection exception handler calls the virtual-8086 monitor, which can then emulate an

8086-program interrupt handler or pass control back to the 8086 program’s handler, as described in Section

20.3.1.2, “Handling an Interrupt or Exception With an 8086 Program Interrupt or Exception Handler”.

Method 3 is enabled when the VME flag is set to 1, the IOPL value is less than 3, and the corresponding bit for the

software interrupt in the software interrupt redirection bit map is set to 1. Here, the processor performs the same

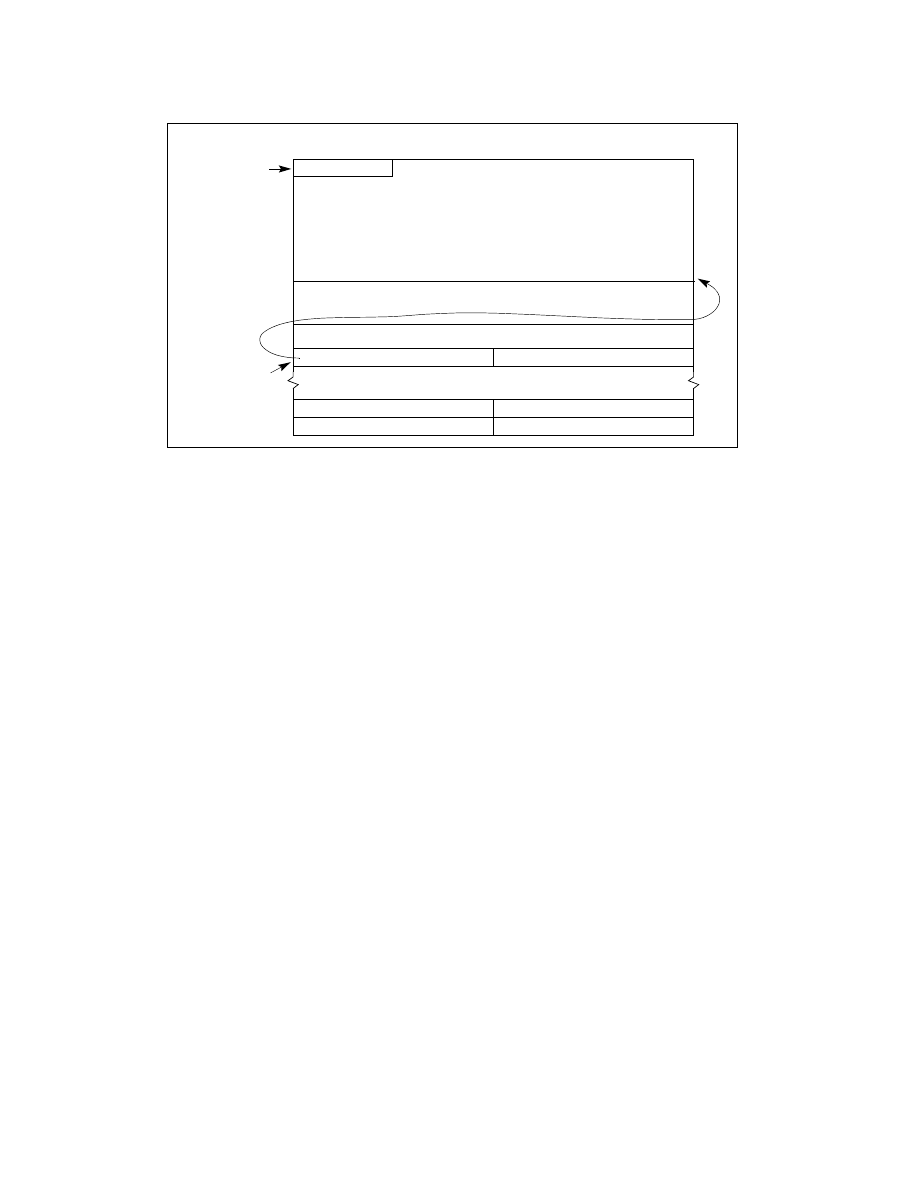

Figure 20-5. Software Interrupt Redirection Bit Map in TSS

I/O Map Base

Task-State Segment (TSS)

64H

31

24 23

0

1

1

1

1

1

1

1

1

I/O Permission Bit Map

0

I/O map

base must

not exceed

DFFFH.

Last byte of

bit

map must be

Software Interrupt Redirection Bit Map (32 Bytes)