Vol. 3B 20-13

8086 EMULATION

3. Clears the segment registers. Saving the DS, ES, FS, and GS registers on the stack and then clearing the

registers lets the interrupt or exception handler safely save and restore these registers regardless of the type

segment selectors they contain (protected-mode or 8086-style). The interrupt and exception handlers, which

may be called in the context of either a protected-mode task or a virtual-8086-mode task, can use the same

code sequences for saving and restoring the registers for any task. Clearing these registers before execution of

the IRET instruction does not cause a trap in the interrupt handler. Interrupt procedures that expect values in

the segment registers or that return values in the segment registers must use the register images saved on the

stack for privilege level 0.

4. Clears VM, NT, RF and TF flags (in the EFLAGS register). If the gate is an interrupt gate, clears the IF flag.

5. Begins executing the selected interrupt or exception handler.

If the trap or interrupt gate references a procedure in a conforming segment or in a segment at a privilege level

other than 0, the processor generates a general-protection exception (#GP). Here, the error code is the segment

selector of the code segment to which a call was attempted.

Interrupt and exception handlers can examine the VM flag on the stack to determine if the interrupted procedure

was running in virtual-8086 mode. If so, the interrupt or exception can be handled in one of three ways:

•

The protected-mode interrupt or exception handler that was called can handle the interrupt or exception.

•

The protected-mode interrupt or exception handler can call the virtual-8086 monitor to handle the interrupt or

exception.

•

The virtual-8086 monitor (if called) can in turn pass control back to the 8086 program’s interrupt and exception

handler.

If the interrupt or exception is handled with a protected-mode handler, the handler can return to the interrupted

program in virtual-8086 mode by executing an IRET instruction. This instruction loads the EFLAGS and segment

registers from the images saved in the privilege level 0 stack (see Figure 20-4). A set VM flag in the EFLAGS image

causes the processor to switch back to virtual-8086 mode. The CPL at the time the IRET instruction is executed

must be 0, otherwise the processor does not change the state of the VM flag.

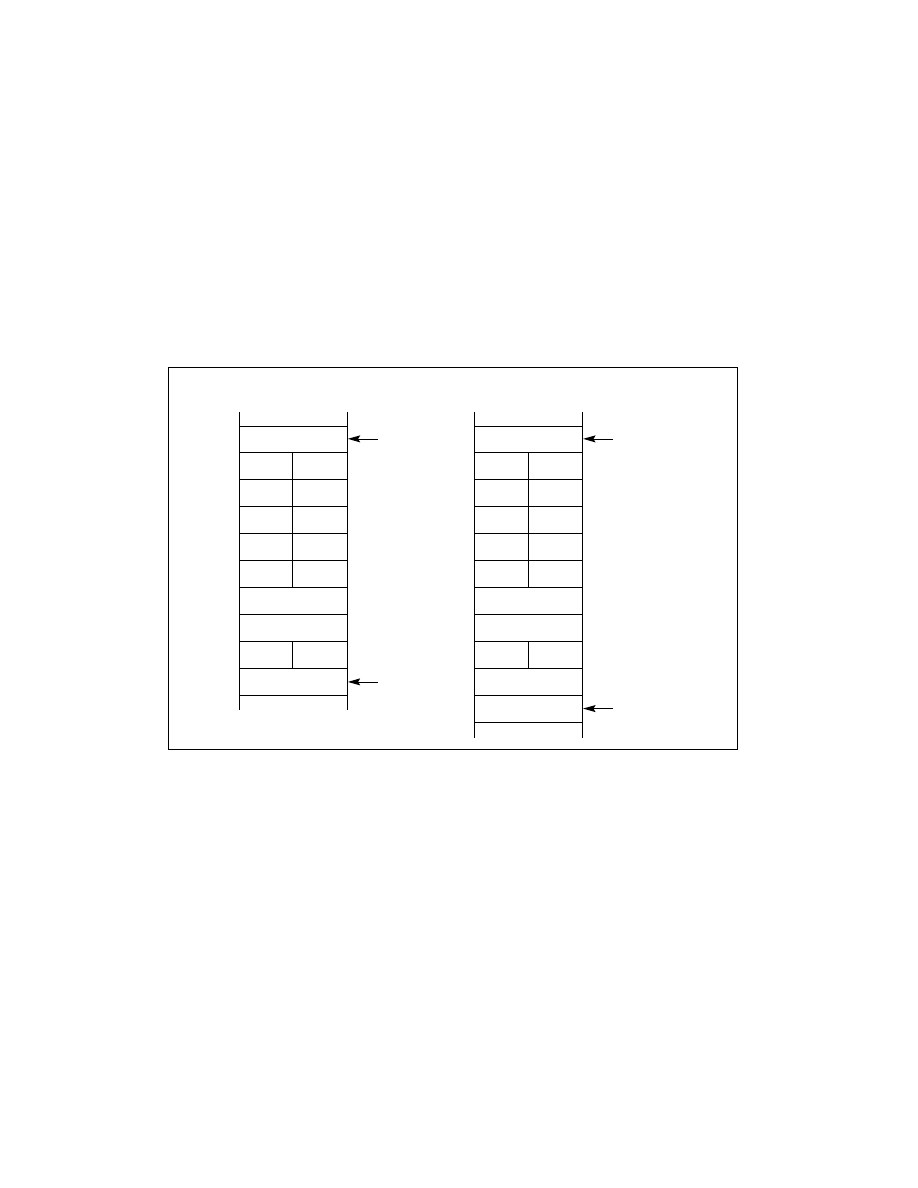

Figure 20-4. Privilege Level 0 Stack After Interrupt or

Exception in Virtual-8086 Mode

Unused

Old GS

Old ESP

With Error Code

ESP from

Old FS

Old DS

Old ES

Old SS

Old EFLAGS

Old CS

Old EIP

Error Code

New ESP

TSS

Unused

Old GS

Old ESP

Without Error Code

ESP from

Old FS

Old DS

Old ES

Old SS

Old EFLAGS

Old CS

Old EIP

New ESP

TSS