Vol. 3B 20-5

8086 EMULATION

5. Transfers program control to the location specified in the interrupt vector table.

An IRET instruction at the end of the handler procedure reverses these steps to return program control to the inter-

rupted program. Exceptions do not return error codes in real-address mode.

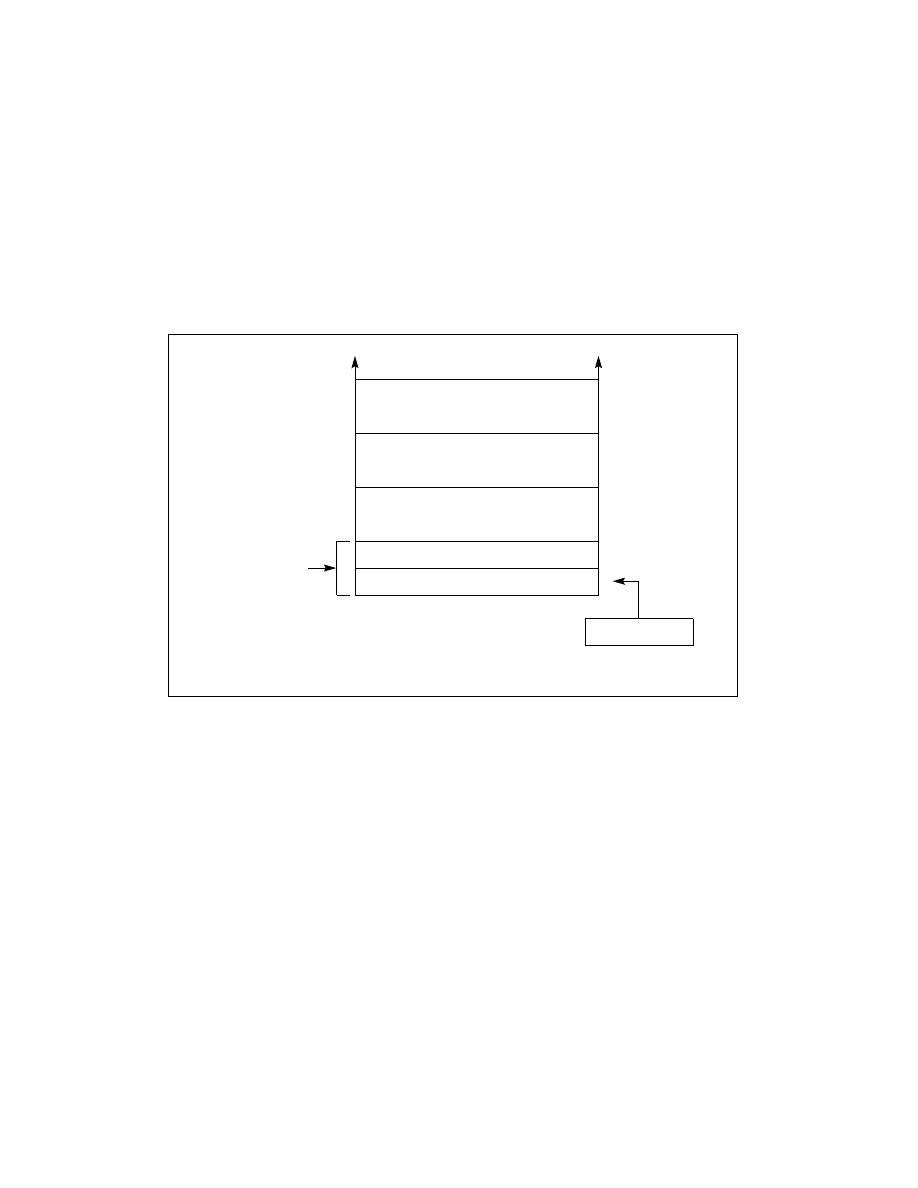

The interrupt vector table is an array of 4-byte entries (see Figure 20-2). Each entry consists of a far pointer to a

handler procedure, made up of a segment selector and an offset. The processor scales the interrupt or exception

vector by 4 to obtain an offset into the interrupt table. Following reset, the base of the interrupt vector table is

located at physical address 0 and its limit is set to 3FFH. In the Intel 8086 processor, the base address and limit of

the interrupt vector table cannot be changed. In the later IA-32 processors, the base address and limit of the inter-

rupt vector table are contained in the IDTR register and can be changed using the LIDT instruction.

(For backward compatibility to Intel 8086 processors, the default base address and limit of the interrupt vector

table should not be changed.)

Table 20-1 shows the interrupt and exception vectors that can be generated in real-address mode and virtual-8086

mode, and in the Intel 8086 processor. See Chapter 6, “Interrupt and Exception Handling”, for a description of the

exception conditions.

20.2 VIRTUAL-8086

MODE

Virtual-8086 mode is actually a special type of a task that runs in protected mode. When the operating-system or

executive switches to a virtual-8086-mode task, the processor emulates an Intel 8086 processor. The execution

environment of the processor while in the 8086-emulation state is the same as is described in Section 20.1, “Real-

Address Mode” for real-address mode, including the extensions. The major difference between the two modes is

that in virtual-8086 mode the 8086 emulator uses some protected-mode services (such as the protected-mode

interrupt and exception-handling and paging facilities).

Figure 20-2. Interrupt Vector Table in Real-Address Mode

0

2

4

8

12

0

15

Segment Selector

Offset

* Interrupt vector number 0 selects entry 0

Interrupt Vector 0*

Entry 1

Entry 2

Entry 3

Up to Entry 255

IDTR

(called “interrupt vector 0”) in the interrupt

vector table. Interrupt vector 0 in turn

points to the start of the interrupt handler

for interrupt 0.