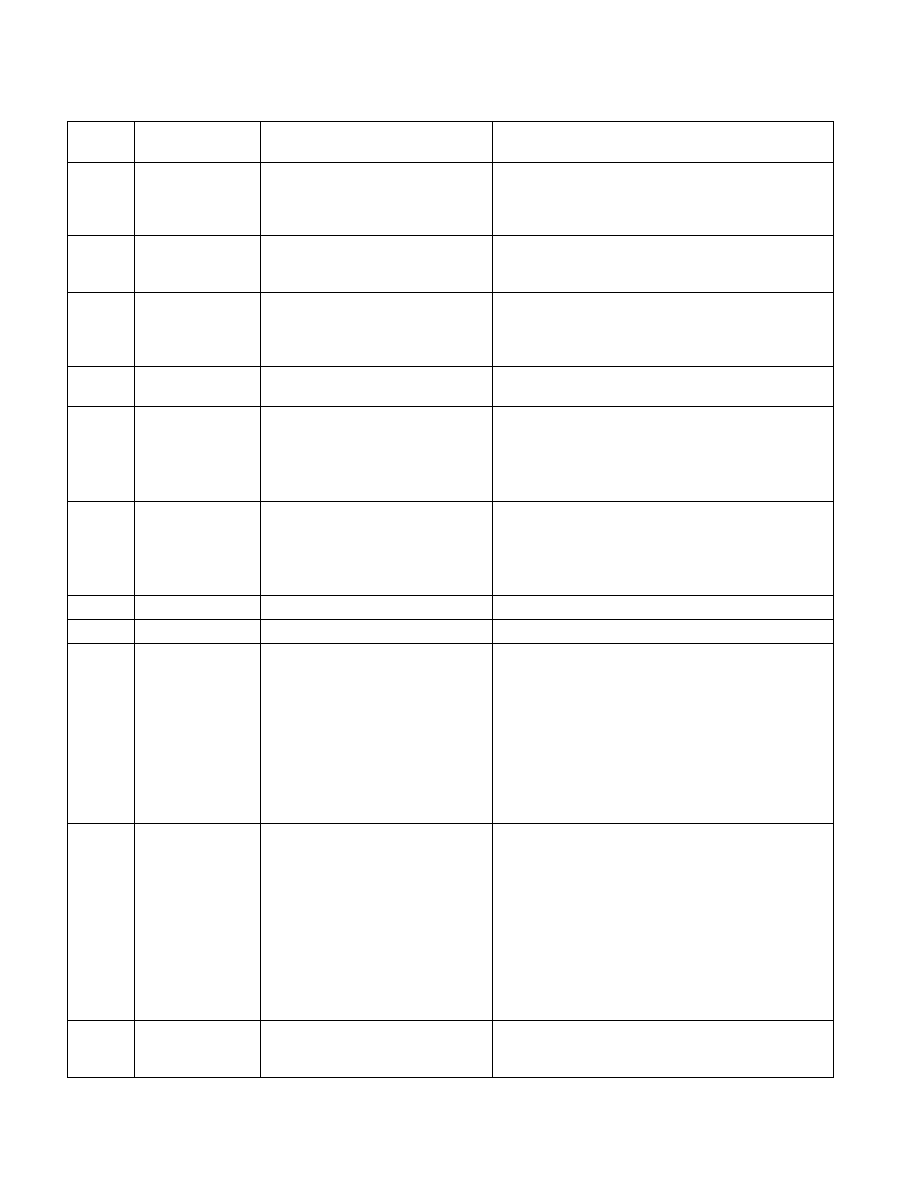

19-216 Vol. 3B

PERFORMANCE-MONITORING EVENTS

1AH

WAITING_FOR_

DATA_MEMORY_

READ_STALL_

DURATION

Number of clocks while the pipeline is

stalled while waiting for data memory

reads.

Data TLB Miss processing is also included in the count. The

pipeline stalls while a data memory read is in progress

including attempts to read that are not bypassed while a

line is being filled.

1BH

STALL ON WRITE

TO AN E- OR M-

STATE LINE

Number of stalls on writes to E- or M-

state lines.

1CH

LOCKED BUS CYCLE Number of locked bus cycles that occur

as the result of the LOCK prefix or

LOCK instruction, page-table updates,

and descriptor table updates.

Only the read portion of the locked read-modify-write is

counted. Split locked cycles (SCYC active) count as two

separate accesses. Cycles restarted due to BOFF# are not

re-counted.

1DH

I/O READ OR WRITE

CYCLE

Number of bus cycles directed to I/O

space.

Misaligned I/O accesses will generate two bus cycles. Bus

cycles restarted due to BOFF# are not re-counted.

1EH

NONCACHEABLE_

MEMORY_READS

Number of noncacheable instruction or

data memory read bus cycles.

The count includes read cycles caused

by TLB misses, but does not include

read cycles to I/O space.

Cycles restarted due to BOFF# are not re-counted.

1FH

PIPELINE_AGI_

STALLS

Number of address generation

interlock (AGI) stalls.

An AGI occurring in both the U- and V-

pipelines in the same clock signals this

event twice.

An AGI occurs when the instruction in the execute stage

of either of U- or V-pipelines is writing to either the index

or base address register of an instruction in the D2

(address generation) stage of either the U- or V- pipelines.

20H

Reserved

21H

Reserved

22H

FLOPS

Number of floating-point operations

that occur.

Number of floating-point adds, subtracts, multiplies,

divides, remainders, and square roots are counted. The

transcendental instructions consist of multiple adds and

multiplies and will signal this event multiple times.

Instructions generating the divide-by-zero, negative

square root, special operand, or stack exceptions will not

be counted.

Instructions generating all other floating-point exceptions

will be counted. The integer multiply instructions and

other instructions which use the x87 FPU will be counted.

23H

BREAKPOINT

MATCH ON DR0

REGISTER

Number of matches on register DR0

breakpoint.

The counters is incremented regardless if the breakpoints

are enabled or not. However, if breakpoints are not

enabled, code breakpoint matches will not be checked for

instructions executed in the V-pipe and will not cause this

counter to be incremented. (They are checked on

instruction executed in the U-pipe only when breakpoints

are not enabled.)

These events correspond to the signals driven on the

BP[3:0] pins. Refer to Chapter 17, “Debug, Branch Profile,

TSC, and Resource Monitoring Features” for more

information.

24H

BREAKPOINT

MATCH ON DR1

REGISTER

Number of matches on register DR1

breakpoint.

See comment for 23H event.

Table 19-38. Events That Can Be Counted with Pentium Processor Performance-Monitoring Counters (Contd.)

Event

Num.

Mnemonic Event

Name

Description

Comments