Vol. 3B 19-213

PERFORMANCE-MONITORING EVENTS

19.18 PENTIUM PROCESSOR PERFORMANCE-MONITORING EVENTS

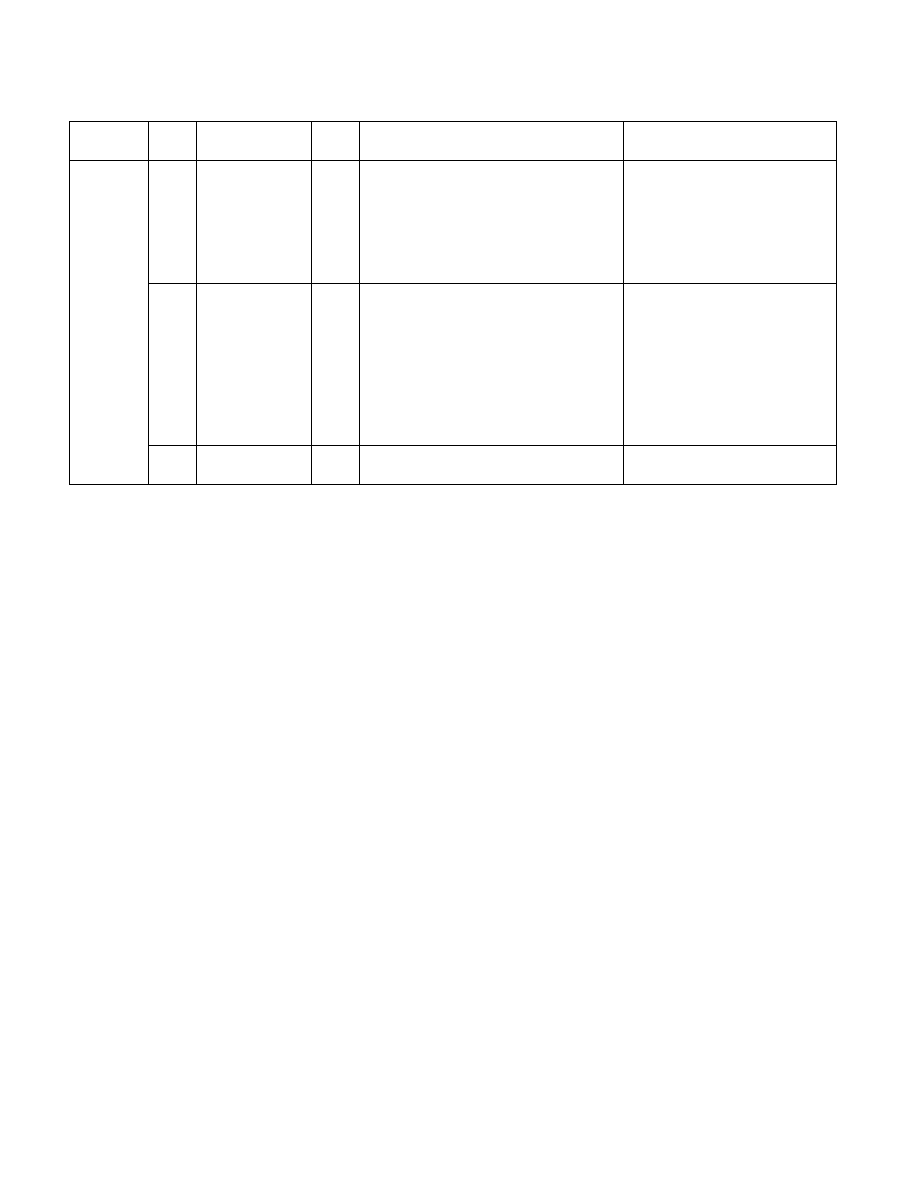

Table 19-38 lists the events that can be counted with the performance-monitoring counters for the Pentium

processor. The Event Number column gives the hexadecimal code that identifies the event and that is entered in

the ES0 or ES1 (event select) fields of the CESR MSR. The Mnemonic Event Name column gives the name of the

event, and the Description and Comments columns give detailed descriptions of the events. Most events can be

counted with either counter 0 or counter 1; however, some events can only be counted with only counter 0 or only

counter 1 (as noted).

NOTE

The events in the table that are shaded are implemented only in the Pentium processor with MMX

technology.

02H

04H

08H

0FH

Segment register ES

Segment register DS

Segment register FS

Segment register FS

Segment registers

ES + DS + FS + GS

D5H

SEG_REG_

RENAMES

Number of Segment Register Renames:

Available in Pentium

II and Pentium

III processors only.

01H

02H

04H

08H

0FH

Segment register ES

Segment register DS

Segment register FS

Segment register FS

Segment registers

ES + DS + FS + GS

D6H

RET_SEG_

RENAMES

00H

Number of segment register rename events

retired.

Available in Pentium

II and Pentium

III processors only.

NOTES:

1. Several L2 cache events, where noted, can be further qualified using the Unit Mask (UMSK) field in the PerfEvtSel0 and

PerfEvtSel1 registers. The lower 4 bits of the Unit Mask field are used in conjunction with L2 events to indicate the cache state or

cache states involved.

The P6 family processors identify cache states using the “MESI” protocol and consequently each bit in the Unit Mask field repre-

sents one of the four states: UMSK[3] = M (8H) state, UMSK[2] = E (4H) state, UMSK[1] = S (2H) state, and UMSK[0] = I (1H) state.

UMSK[3:0] = MESI” (FH) should be used to collect data for all states; UMSK = 0H, for the applicable events, will result in nothing

being counted.

2. All of the external bus logic (EBL) events, except where noted, can be further qualified using the Unit Mask (UMSK) field in the

PerfEvtSel0 and PerfEvtSel1 registers.

Bit 5 of the UMSK field is used in conjunction with the EBL events to indicate whether the processor should count transactions that

are self- generated (UMSK[5] = 0) or transactions that result from any processor on the bus (UMSK[5] = 1).

3. L2 cache locks, so it is possible to have a zero count.

Table 19-37. Events That Can Be Counted with the P6 Family Performance-Monitoring Counters (Contd.)

Unit

Event

Num.

Mnemonic Event

Name

Unit

Mask Description

Comments