19-214 Vol. 3B

PERFORMANCE-MONITORING EVENTS

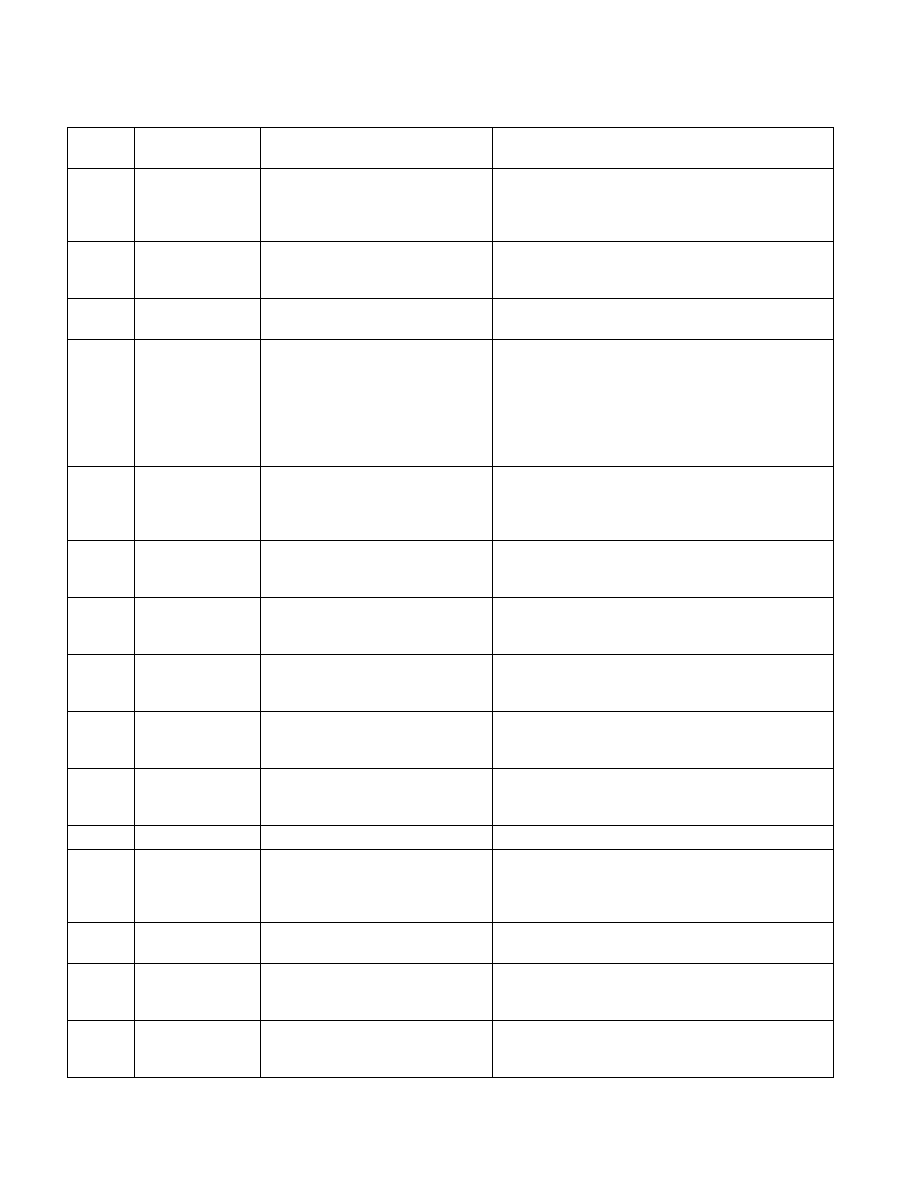

Table 19-38. Events That Can Be Counted with Pentium Processor Performance-Monitoring Counters

Event

Num.

Mnemonic Event

Name

Description

Comments

00H

DATA_READ

Number of memory data reads

(internal data cache hit and miss

combined).

Split cycle reads are counted individually. Data Memory

Reads that are part of TLB miss processing are not

included. These events may occur at a maximum of two

per clock. I/O is not included.

01H

DATA_WRITE

Number of memory data writes

(internal data cache hit and miss

combined); I/O not included.

Split cycle writes are counted individually. These events

may occur at a maximum of two per clock. I/O is not

included.

0H2

DATA_TLB_MISS

Number of misses to the data cache

translation look-aside buffer.

03H

DATA_READ_MISS

Number of memory read accesses that

miss the internal data cache whether

or not the access is cacheable or

noncacheable.

Additional reads to the same cache line after the first

BRDY# of the burst line fill is returned but before the final

(fourth) BRDY# has been returned, will not cause the

counter to be incremented additional times.

Data accesses that are part of TLB miss processing are

not included. Accesses directed to I/O space are not

included.

04H

DATA WRITE MISS

Number of memory write accesses

that miss the internal data cache

whether or not the access is cacheable

or noncacheable.

Data accesses that are part of TLB miss processing are

not included. Accesses directed to I/O space are not

included.

05H

WRITE_HIT_TO_

M-_OR_E-

STATE_LINES

Number of write hits to exclusive or

modified lines in the data cache.

These are the writes that may be held up if EWBE# is

inactive. These events may occur a maximum of two per

clock.

06H

DATA_CACHE_

LINES_

WRITTEN_BACK

Number of dirty lines (all) that are

written back, regardless of the cause.

Replacements and internal and external snoops can all

cause writeback and are counted.

07H

EXTERNAL_

SNOOPS

Number of accepted external snoops

whether they hit in the code cache or

data cache or neither.

Assertions of EADS# outside of the sampling interval are

not counted, and no internal snoops are counted.

08H

EXTERNAL_DATA_

CACHE_SNOOP_

HITS

Number of external snoops to the data

cache.

Snoop hits to a valid line in either the data cache, the data

line fill buffer, or one of the write back buffers are all

counted as hits.

09H

MEMORY ACCESSES

IN BOTH PIPES

Number of data memory reads or

writes that are paired in both pipes of

the pipeline.

These accesses are not necessarily run in parallel due to

cache misses, bank conflicts, etc.

0AH

BANK CONFLICTS

Number of actual bank conflicts.

0BH

MISALIGNED DATA

MEMORY OR I/O

REFERENCES

Number of memory or I/O reads or

writes that are misaligned.

A 2- or 4-byte access is misaligned when it crosses a 4-

byte boundary; an 8-byte access is misaligned when it

crosses an 8-byte boundary. Ten byte accesses are

treated as two separate accesses of 8 and 2 bytes each.

0CH

CODE READ

Number of instruction reads; whether

the read is cacheable or noncacheable.

Individual 8-byte noncacheable instruction reads are

counted.

0DH

CODE TLB MISS

Number of instruction reads that miss

the code TLB whether the read is

cacheable or noncacheable.

Individual 8-byte noncacheable instruction reads are

counted.

0EH

CODE CACHE MISS

Number of instruction reads that miss

the internal code cache; whether the

read is cacheable or noncacheable.

Individual 8-byte noncacheable instruction reads are

counted.