3-8 Vol. 3A

PROTECTED-MODE MEMORY MANAGEMENT

Requested Privilege Level (RPL)

(Bits 0 and 1) — Specifies the privilege level of the selector. The privilege level can range from 0 to

3, with 0 being the most privileged level. See Section 5.5, “Privilege Levels”, for a description of the

relationship of the RPL to the CPL of the executing program (or task) and the descriptor privilege

level (DPL) of the descriptor the segment selector points to.

The first entry of the GDT is not used by the processor. A segment selector that points to this entry of the GDT (that

is, a segment selector with an index of 0 and the TI flag set to 0) is used as a “null segment selector.” The processor

does not generate an exception when a segment register (other than the CS or SS registers) is loaded with a null

selector. It does, however, generate an exception when a segment register holding a null selector is used to access

memory. A null selector can be used to initialize unused segment registers. Loading the CS or SS register with a null

segment selector causes a general-protection exception (#GP) to be generated.

Segment selectors are visible to application programs as part of a pointer variable, but the values of selectors are

usually assigned or modified by link editors or linking loaders, not application programs.

3.4.3 Segment

Registers

To reduce address translation time and coding complexity, the processor provides registers for holding up to 6

segment selectors (see Figure 3-7). Each of these segment registers support a specific kind of memory reference

(code, stack, or data). For virtually any kind of program execution to take place, at least the code-segment (CS),

data-segment (DS), and stack-segment (SS) registers must be loaded with valid segment selectors. The processor

also provides three additional data-segment registers (ES, FS, and GS), which can be used to make additional data

segments available to the currently executing program (or task).

For a program to access a segment, the segment selector for the segment must have been loaded in one of the

segment registers. So, although a system can define thousands of segments, only 6 can be available for immediate

use. Other segments can be made available by loading their segment selectors into these registers during program

execution.

Every segment register has a “visible” part and a “hidden” part. (The hidden part is sometimes referred to as a

“descriptor cache” or a “shadow register.”) When a segment selector is loaded into the visible part of a segment

register, the processor also loads the hidden part of the segment register with the base address, segment limit, and

access control information from the segment descriptor pointed to by the segment selector. The information cached

in the segment register (visible and hidden) allows the processor to translate addresses without taking extra bus

cycles to read the base address and limit from the segment descriptor. In systems in which multiple processors

have access to the same descriptor tables, it is the responsibility of software to reload the segment registers when

the descriptor tables are modified. If this is not done, an old segment descriptor cached in a segment register might

be used after its memory-resident version has been modified.

Two kinds of load instructions are provided for loading the segment registers:

1. Direct load instructions such as the MOV, POP, LDS, LES, LSS, LGS, and LFS instructions. These instructions

explicitly reference the segment registers.

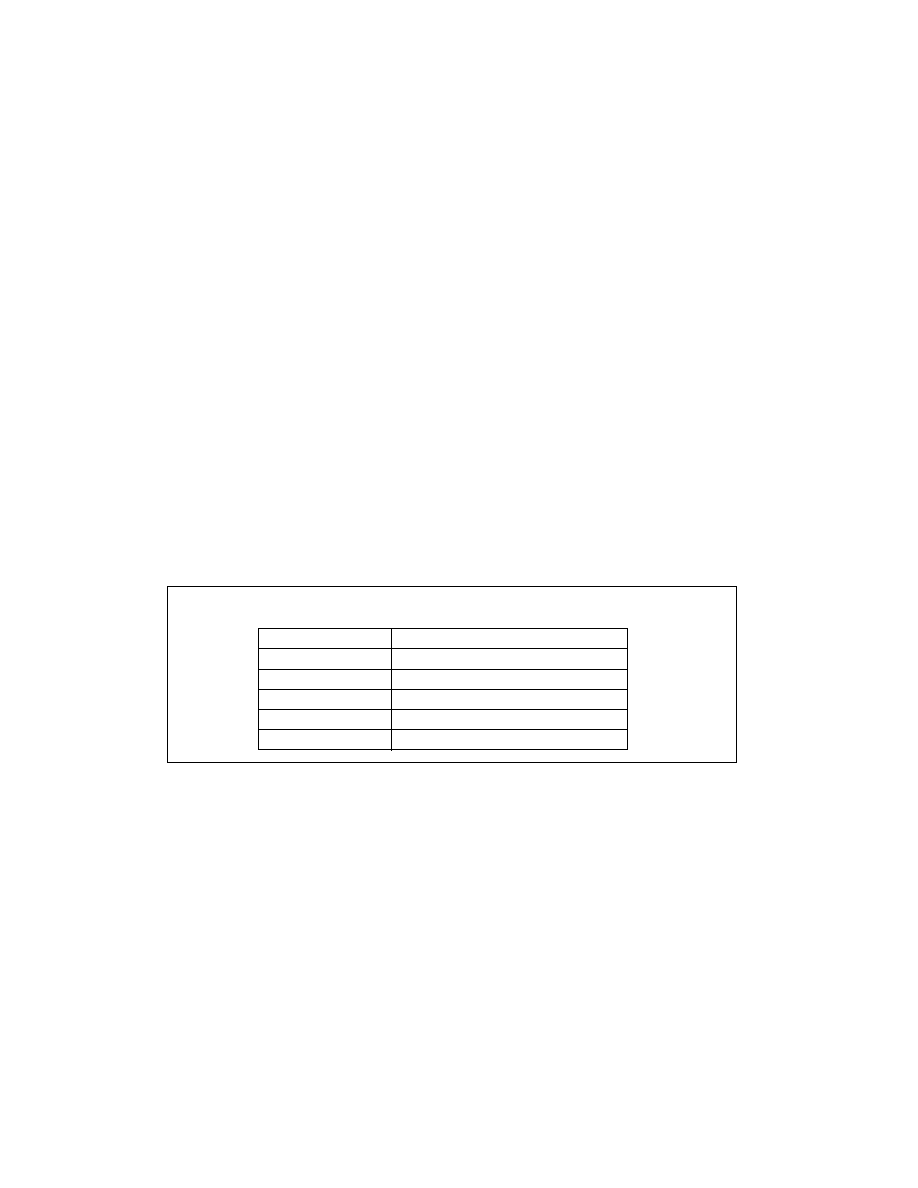

Figure 3-7. Segment Registers

CS

SS

DS

ES

FS

GS

Segment Selector

Base Address, Limit, Access Information

Visible Part

Hidden Part