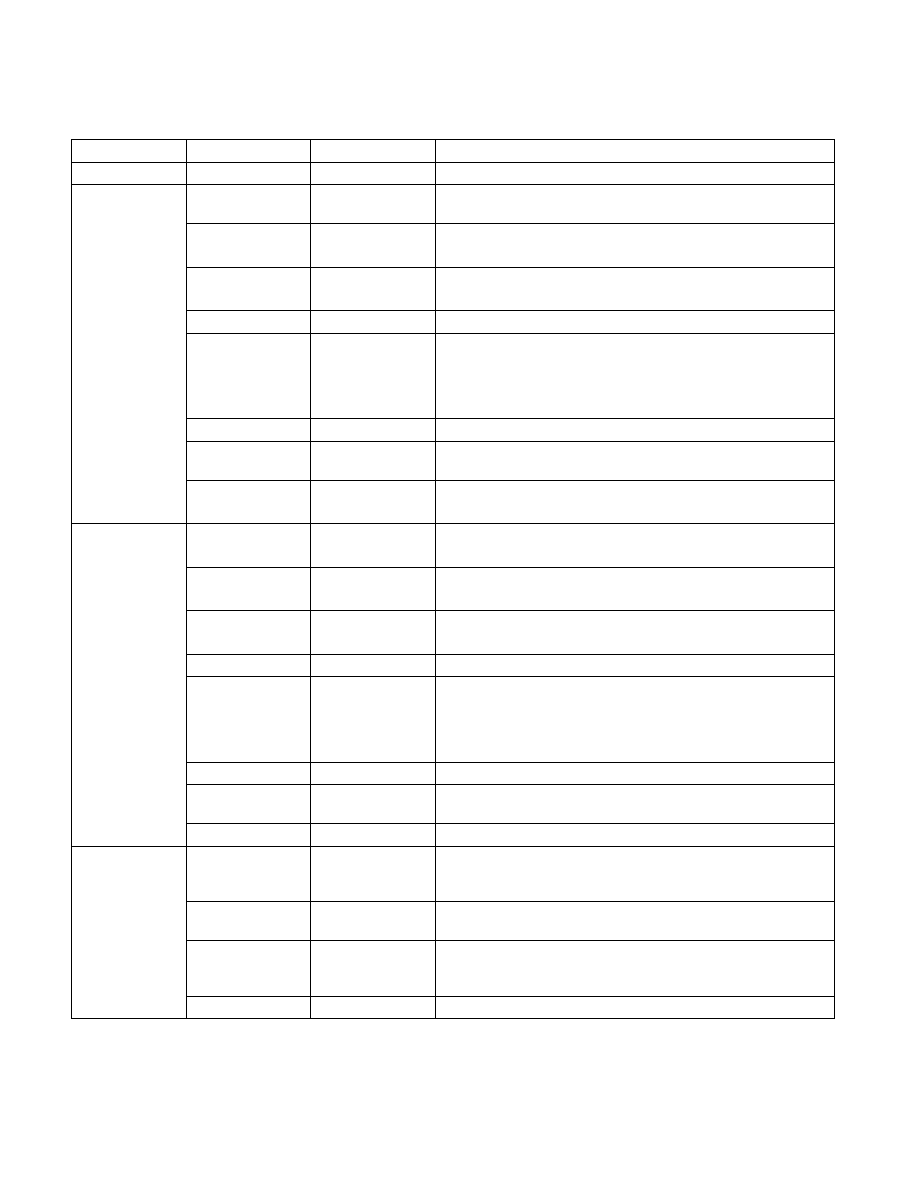

Vol. 3B 19-193

PERFORMANCE-MONITORING EVENTS

Can Support PEBS

No

uops_retired This

event

counts

μops that are retired during a clock cycle. Mask bits

specify bogus or non-bogus.

ESCR restrictions

MSR_CRU_ESCR0

MSR_CRU_ESCR1

Counter numbers

per ESCR

ESCR0: 12, 13, 16

ESCR1: 14, 15, 17

ESCR Event Select

01H

ESCR[31:25]

ESCR Event Mask

Bit

0: NBOGUS

1: BOGUS

ESCR[24:9]

The marked μops are not bogus.

The marked μops are bogus.

CCCR Select

04H

CCCR[15:13]

Event Specific

Notes

P6: EMON_UOPS_RETIRED

Can Support PEBS

No

uop_type

This event is used in conjunction with the front-end at-retirement

mechanism to tag load and store μops.

ESCR restrictions

MSR_RAT_ESCR0

MSR_RAT_ESCR1

Counter numbers

per ESCR

ESCR0: 12, 13, 16

ESCR1: 14, 15, 17

ESCR Event Select

02H

ESCR[31:25]

ESCR Event Mask

Bit

1: TAGLOADS

2: TAGSTORES

ESCR[24:9]

The μop is a load operation.

The μop is a store operation.

CCCR Select

02H

CCCR[15:13]

Event Specific

Notes

Setting the TAGLOADS and TAGSTORES mask bits does not cause a

counter to increment. They are only used to tag uops.

Can Support PEBS

No

branch_retired

This event counts the retirement of a branch. Specify one or more

mask bits to select any combination of taken, not-taken, predicted

and mispredicted.

ESCR restrictions

MSR_CRU_ESCR2

MSR_CRU_ESCR3

See Table 18-63 for the addresses of the ESCR MSRs

Counter numbers

per ESCR

ESCR2: 12, 13, 16

ESCR3: 14, 15, 17

The counter numbers associated with each ESCR are provided. The

performance counters and corresponding CCCRs can be obtained

from Table 18-63.

ESCR Event Select

06H

ESCR[31:25]

Table 19-29. Performance Monitoring Events For Intel NetBurst® Microarchitecture

for At-Retirement Counting (Contd.)

Event Name

Event Parameters

Parameter Value

Description