19-168 Vol. 3B

PERFORMANCE-MONITORING EVENTS

19.14 PERFORMANCE MONITORING EVENTS FOR INTEL

®

CORE

™

SOLO AND

INTEL

®

CORE

™

DUO PROCESSORS

Table 19-27 lists non-architectural performance events for Intel

®

Core™ Duo processors. If a non-architectural

event requires qualification in core specificity, it is indicated in the comment column. Table 19-27 also applies to

Intel

®

Core™ Solo processors; bits in the unit mask corresponding to core-specificity are reserved and should be

00B.

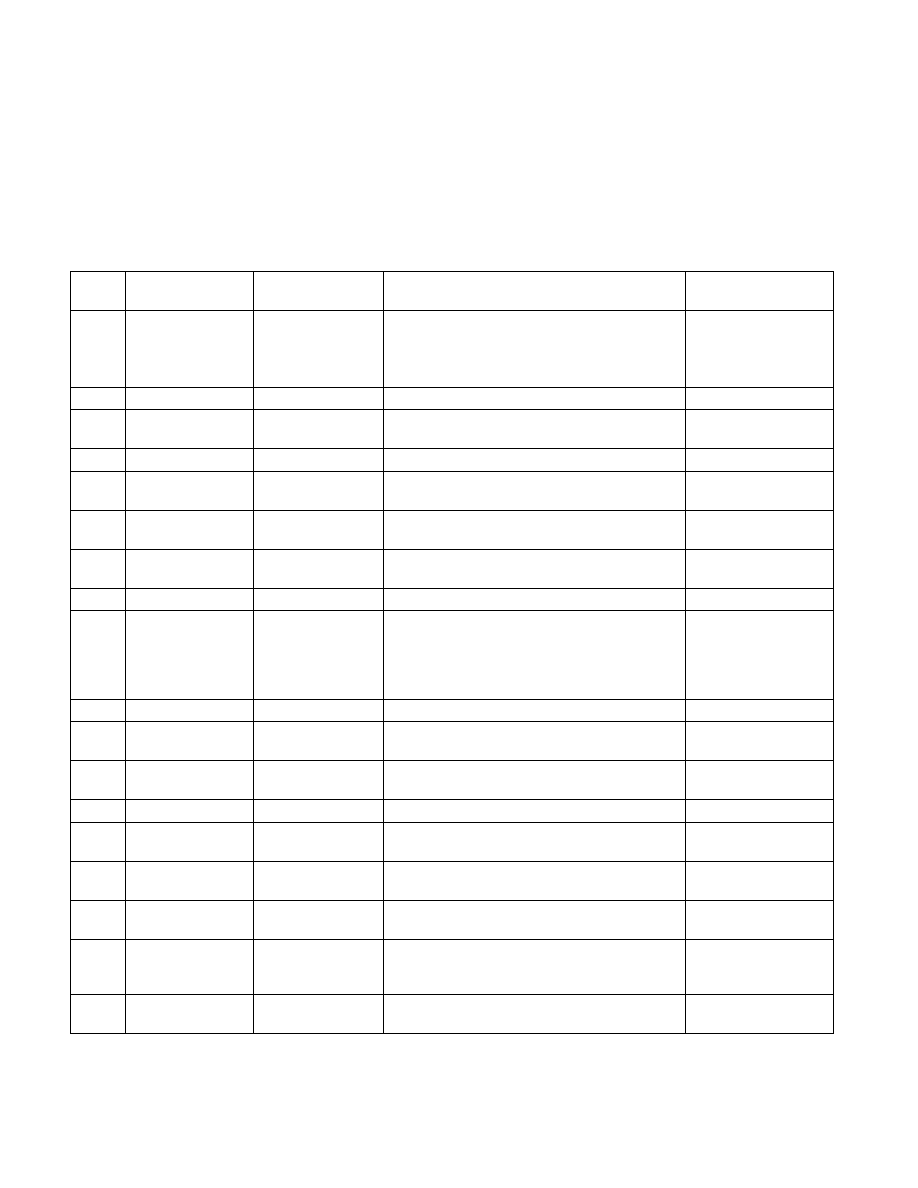

Table 19-27. Non-Architectural Performance Events in Intel® Core™ Solo and Intel® Core™ Duo Processors

Event

Num.

Event Mask

Mnemonic

Umask

Value

Description

Comment

03H

LD_Blocks

00H

Load operations delayed due to store buffer blocks.

The preceding store may be blocked due to

unknown address, unknown data, or conflict due to

partial overlap between the load and store.

04H

SD_Drains

00H

Cycles while draining store buffers.

05H

Misalign_Mem_Ref

00H

Misaligned data memory references (MOB splits of

loads and stores).

06H

Seg_Reg_Loads

00H

Segment register loads.

07H

SSE_PrefNta_Ret

00H

SSE software prefetch instruction PREFETCHNTA

retired.

07H

SSE_PrefT1_Ret

01H

SSE software prefetch instruction PREFETCHT1

retired.

07H

SSE_PrefT2_Ret

02H

SSE software prefetch instruction PREFETCHT2

retired.

07H

SSE_NTStores_Ret

03H

SSE streaming store instruction retired.

10H

FP_Comps_Op_Exe

00H

FP computational Instruction executed. FADD,

FSUB, FCOM, FMULs, MUL, IMUL, FDIVs, DIV, IDIV,

FPREMs, FSQRT are included; but exclude FADD or

FMUL used in the middle of a transcendental

instruction.

11H

FP_Assist

00H

FP exceptions experienced microcode assists.

IA32_PMC1 only.

12H

Mul

00H

Multiply operations (a speculative count, including

FP and integer multiplies).

IA32_PMC1 only.

13H

Div

00H

Divide operations (a speculative count, including FP

and integer divisions).

IA32_PMC1 only.

14H

Cycles_Div_Busy

00H

Cycles the divider is busy.

IA32_PMC0 only.

21H

L2_ADS

00H

L2 Address strobes.

Requires core-

specificity.

22H

Dbus_Busy

00H

Core cycle during which data bus was busy

(increments by 4).

Requires core-

specificity.

23H

Dbus_Busy_Rd

00H

Cycles data bus is busy transferring data to a core

(increments by 4).

Requires core-

specificity.

24H

L2_Lines_In

00H

L2 cache lines allocated.

Requires core-specificity

and HW prefetch

qualification.

25H

L2_M_Lines_In

00H

L2 Modified-state cache lines allocated.

Requires core-

specificity.