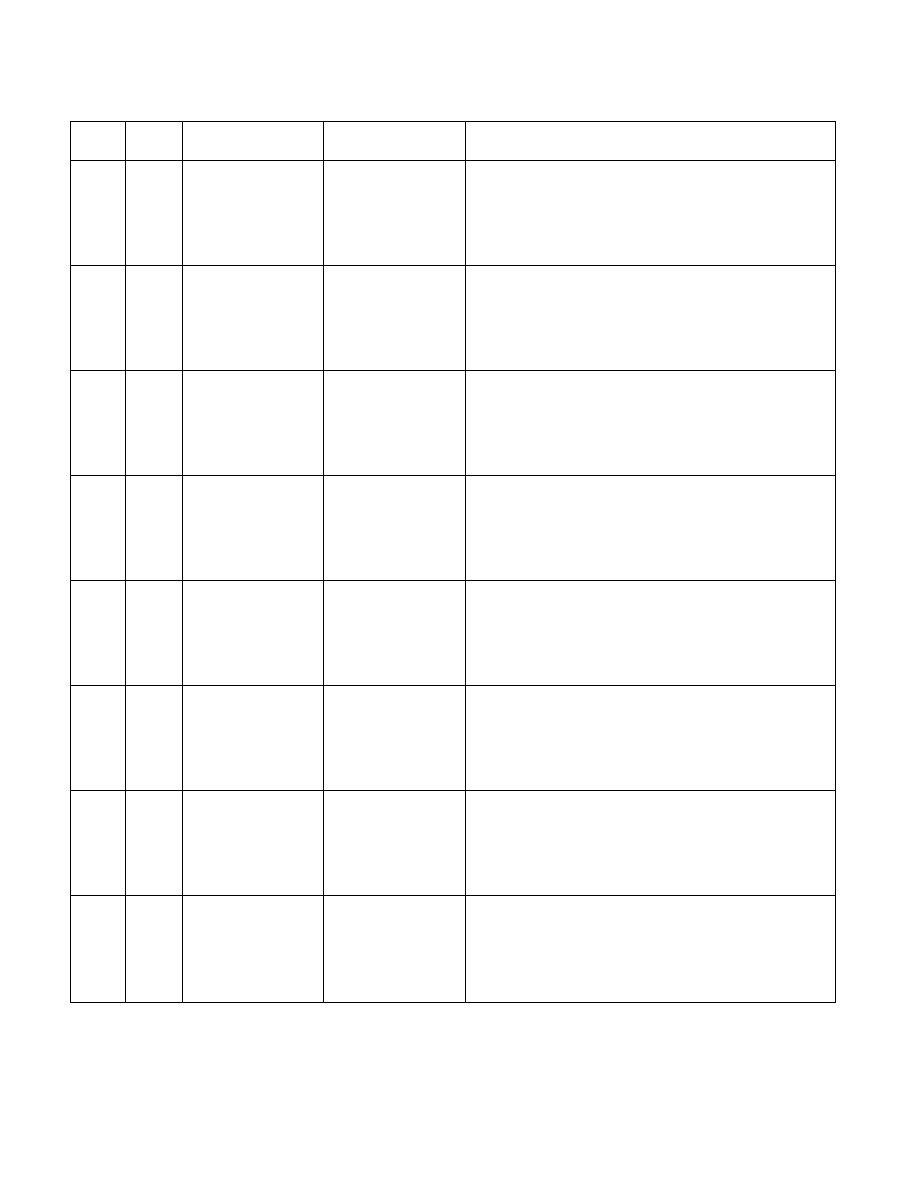

Vol. 3B 19-161

PERFORMANCE-MONITORING EVENTS

67H

See

and

BUS_TRANS_WB

Explicit writeback bus

transactions.

This event counts all explicit writeback bus transactions due to

dirty line evictions. It does not count implicit writebacks due to

invalidation by a snoop request.

68H

See

and

BUS_TRANS_IFETCH

Instruction-fetch bus

transactions.

This event counts all instruction fetch full cache line bus

transactions.

69H

See

and

BUS_TRANS_INVAL

Invalidate bus

transactions.

This event counts all invalidate transactions. Invalidate

transactions are generated when:

- A store operation hits a shared line in the L2 cache.

- A full cache line write misses the L2 cache or hits a shared line

in the L2 cache.

6AH

See

and

BUS_TRANS_PWR

Partial write bus

transaction.

This event counts partial write bus transactions.

6BH

See

and

BUS_TRANS_P

Partial bus

transactions.

This event counts all (read and write) partial bus transactions.

6CH

See

and

BUS_TRANS_IO

IO bus transactions.

This event counts the number of completed I/O bus

transactions as a result of IN and OUT instructions. The count

does not include memory mapped IO.

6DH

See

and

BUS_TRANS_DEF

Deferred bus

transactions.

This event counts the number of deferred transactions.

6EH

See

and

BUS_TRANS_BURST

Burst (full cache-line)

bus transactions.

This event counts burst (full cache line) transactions including:

- Burst reads.

- RFOs.

- Explicit writebacks.

- Write combine lines.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment