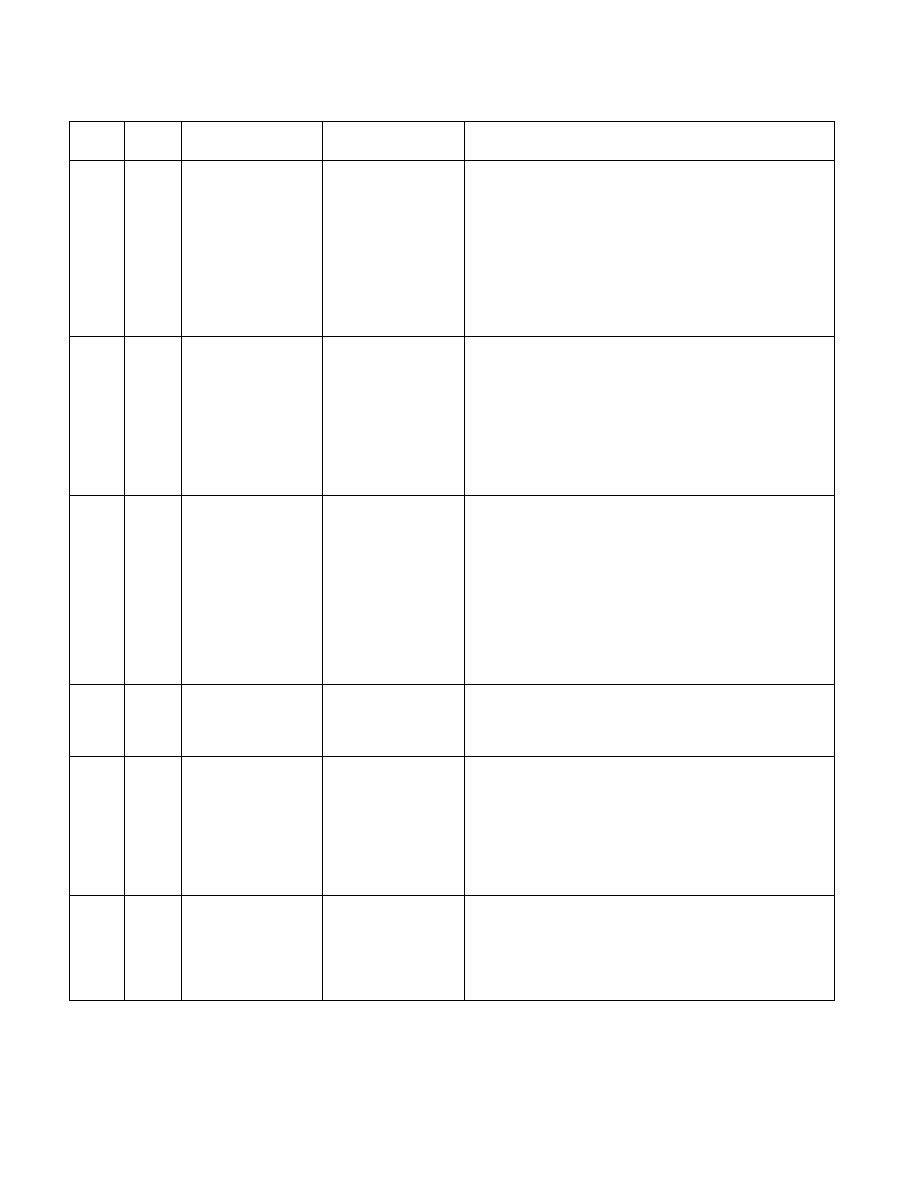

19-160 Vol. 3B

PERFORMANCE-MONITORING EVENTS

61H

See

BUS_BNR_DRV

Number of Bus Not

Ready signals asserted.

This event counts the number of Bus Not Ready (BNR) signals

that the processor asserts on the bus to suspend additional bus

requests by other bus agents. A bus agent asserts the BNR

signal when the number of data and snoop transactions is close

to the maximum that the bus can handle.

While this signal is asserted, new transactions cannot be

submitted on the bus. As a result, transaction latency may have

higher impact on program performance. NOTE: This event is

thread-independent and will not provide a count per logical

processor when AnyThr is disabled.

62H

See

BUS_DRDY_CLOCKS

Bus cycles when data

is sent on the bus.

This event counts the number of bus cycles during which the

DRDY (Data Ready) signal is asserted on the bus. The DRDY

signal is asserted when data is sent on the bus.

This event counts the number of bus cycles during which this

agent (the processor) writes data on the bus back to memory or

to other bus agents. This includes all explicit and implicit data

writebacks, as well as partial writes.

Note: This event is thread-independent and will not provide a

count per logical processor when AnyThr is disabled.

63H

See

and

BUS_LOCK_CLOCKS

Bus cycles when a

LOCK signal is asserted.

This event counts the number of bus cycles, during which the

LOCK signal is asserted on the bus. A LOCK signal is asserted

when there is a locked memory access, due to:

- Uncacheable memory.

- Locked operation that spans two cache lines.

- Page-walk from an uncacheable page table.

Bus locks have a very high performance penalty and it is highly

recommended to avoid such accesses. NOTE: This event is

thread-independent and will not provide a count per logical

processor when AnyThr is disabled.

64H

See

BUS_DATA_RCV

Bus cycles while

processor receives

data.

This event counts the number of cycles during which the

processor is busy receiving data. NOTE: This event is thread-

independent and will not provide a count per logical processor

when AnyThr is disabled.

65H

See

and

BUS_TRANS_BRD

Burst read bus

transactions.

This event counts the number of burst read transactions

including:

- L1 data cache read misses (and L1 data cache hardware

prefetches).

- L2 hardware prefetches by the DPL and L2 streamer.

- IFU read misses of cacheable lines.

It does not include RFO transactions.

66H

See

and

BUS_TRANS_RFO

RFO bus transactions.

This event counts the number of Read For Ownership (RFO) bus

transactions, due to store operations that miss the L1 data

cache and the L2 cache. This event also counts RFO bus

transactions due to locked operations.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment