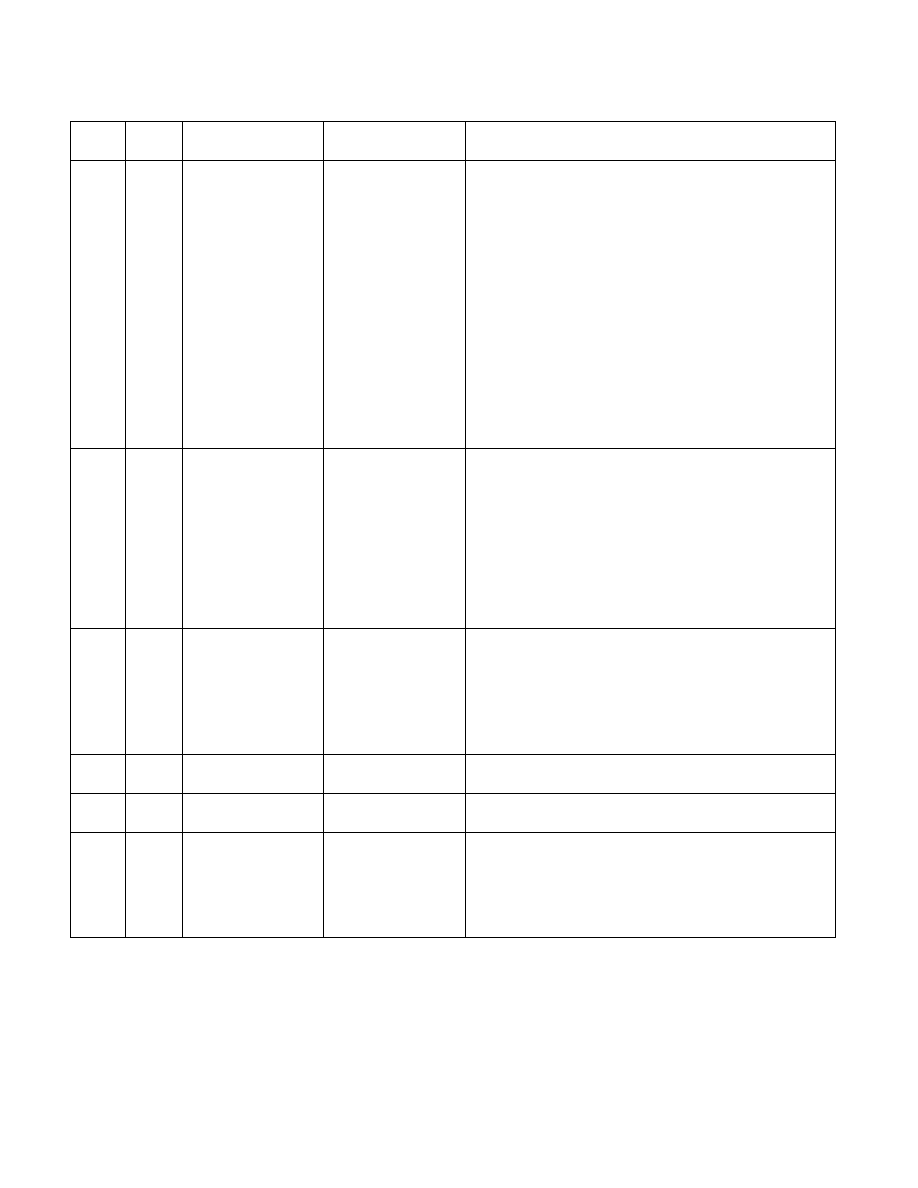

Vol. 3B 19-159

PERFORMANCE-MONITORING EVENTS

3CH

00H

CPU_CLK_UNHALTED.C

ORE_P

Core cycles when core

is not halted.

This event counts the number of core cycles while the core is

not in a halt state. The core enters the halt state when it is

running the HLT instruction. This event is a component in many

key event ratios.

In mobile systems the core frequency may change from time to

time. For this reason this event may have a changing ratio with

regards to time. In systems with a constant core frequency, this

event can give you a measurement of the elapsed time while

the core was not in halt state by dividing the event count by the

core frequency.

-This is an architectural performance event.

- The event CPU_CLK_UNHALTED.CORE_P is counted by a

programmable counter.

- The event CPU_CLK_UNHALTED.CORE is counted by a

designated fixed counter, leaving the two programmable

counters available for other events.

3CH

01H

CPU_CLK_UNHALTED.B

US

Bus cycles when core is

not halted.

This event counts the number of bus cycles while the core is not

in the halt state. This event can give you a measurement of the

elapsed time while the core was not in the halt state, by

dividing the event count by the bus frequency. The core enters

the halt state when it is running the HLT instruction.

The event also has a constant ratio with

CPU_CLK_UNHALTED.REF event, which is the maximum bus to

processor frequency ratio.

Non-halted bus cycles are a component in many key event

ratios.

3CH

02H

CPU_CLK_UNHALTED.

NO_OTHER

Bus cycles when core is

active and the other is

halted.

This event counts the number of bus cycles during which the

core remains non-halted, and the other core on the processor is

halted.

This event can be used to determine the amount of parallelism

exploited by an application or a system. Divide this event count

by the bus frequency to determine the amount of time that

only one core was in use.

40H

21H

L1D_CACHE.LD

L1 Cacheable Data

Reads.

This event counts the number of data reads from cacheable

memory.

40H

22H

L1D_CACHE.ST

L1 Cacheable Data

Writes.

This event counts the number of data writes to cacheable

memory.

60H

See

and

BUS_REQUEST_OUTST

ANDING

Outstanding cacheable

data read bus requests

duration.

This event counts the number of pending full cache line read

transactions on the bus occurring in each cycle. A read

transaction is pending from the cycle it is sent on the bus until

the full cache line is received by the processor. NOTE: This

event is thread-independent and will not provide a count per

logical processor when AnyThr is disabled.

Table 19-26. Non-Architectural Performance Events for 45 nm, 32 nm Intel® Atom™ Processors (Contd.)

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment