Vol. 3A 3-3

PROTECTED-MODE MEMORY MANAGEMENT

programs to multi-segmented models that employ segmentation to create a robust operating environment in

which multiple programs and tasks can be executed reliably.

The following sections give several examples of how segmentation can be employed in a system to improve

memory management performance and reliability.

3.2.1

Basic Flat Model

The simplest memory model for a system is the basic “flat model,” in which the operating system and application

programs have access to a continuous, unsegmented address space. To the greatest extent possible, this basic flat

model hides the segmentation mechanism of the architecture from both the system designer and the application

programmer.

To implement a basic flat memory model with the IA-32 architecture, at least two segment descriptors must be

created, one for referencing a code segment and one for referencing a data segment (see Figure 3-2). Both of

these segments, however, are mapped to the entire linear address space: that is, both segment descriptors have

the same base address value of 0 and the same segment limit of 4 GBytes. By setting the segment limit to 4

GBytes, the segmentation mechanism is kept from generating exceptions for out of limit memory references, even

if no physical memory resides at a particular address. ROM (EPROM) is generally located at the top of the physical

address space, because the processor begins execution at FFFF_FFF0H. RAM (DRAM) is placed at the bottom of the

address space because the initial base address for the DS data segment after reset initialization is 0.

3.2.2

Protected Flat Model

The protected flat model is similar to the basic flat model, except the segment limits are set to include only the

range of addresses for which physical memory actually exists (see Figure 3-3). A general-protection exception

(#GP) is then generated on any attempt to access nonexistent memory. This model provides a minimum level of

hardware protection against some kinds of program bugs.

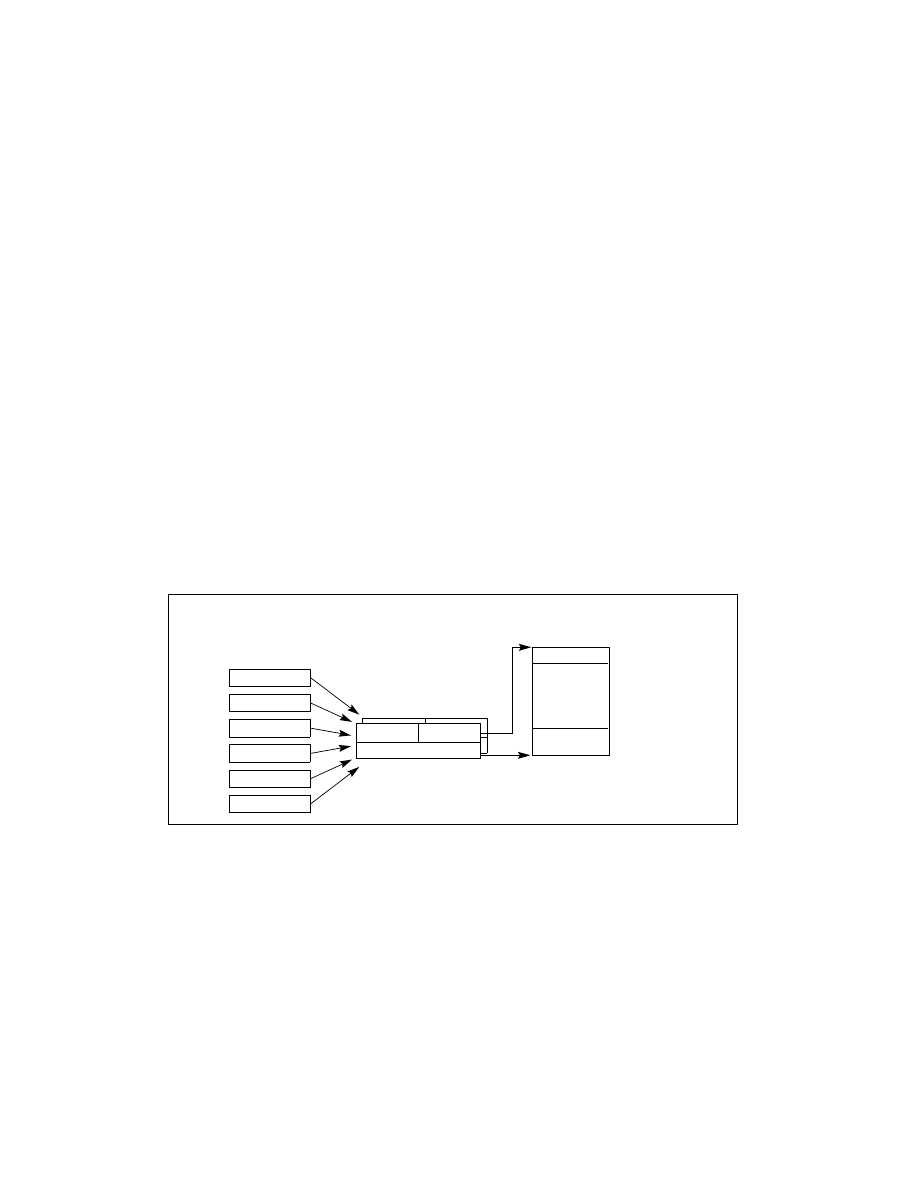

Figure 3-2. Flat Model

Linear Address Space

(or Physical Memory)

Data and

FFFFFFFFH

Segment

Limit

Access

Base Address

Registers

CS

SS

DS

ES

FS

GS

Code

0

Code- and Data-Segment

Descriptors

Stack

Not Present