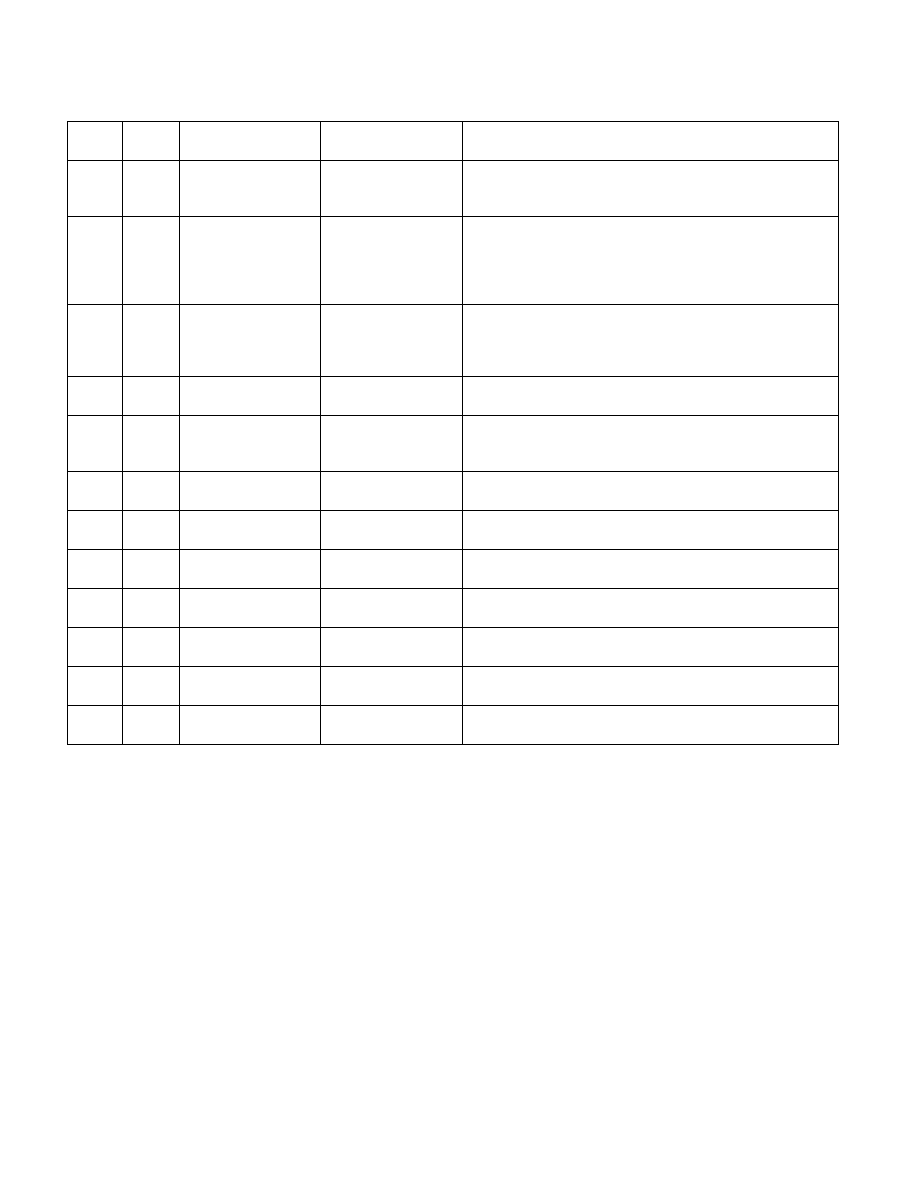

Vol. 3B 19-153

PERFORMANCE-MONITORING EVENTS

19.12.1 Performance Monitoring Events for Processors Based on the Airmont

Microarchitecture

Intel processors based on the Airmont microarchitecture support the same architectural and the non-architectural

performance monitoring events as processors based on the Silvermont microarchitecture. All of the events listed

in Table 19-25 apply

. These processors have the CPUID signatures that include 06_4CH.

C5H

FEH

BR_MISP_RETIRED.TA

KEN_JCC

Retired mispredicted

conditional jumps that

were predicted taken.

This event counts the number of mispredicted branch

instructions retired that were conditional jumps and predicted

taken.

CAH

01H

NO_ALLOC_CYCLES.RO

B_FULL

Counts the number of

cycles when no uops

are allocated and the

ROB is full (less than 2

entries available).

Counts the number of cycles when no uops are allocated and the

ROB is full (less than 2 entries available).

CAH

20H

NO_ALLOC_CYCLES.RA

T_STALL

Counts the number of

cycles when no uops

are allocated and a

RATstall is asserted.

Counts the number of cycles when no uops are allocated and a

RATstall is asserted.

CAH

3FH

NO_ALLOC_CYCLES.AL

L

Front end not

delivering.

This event counts the number of cycles when the front end does

not provide any instructions to be allocated for any reason.

CAH

50H

NO_ALLOC_CYCLES.NO

T_DELIVERED

Front end not

delivering back end not

stalled.

This event counts the number of cycles when the front end does

not provide any instructions to be allocated but the back end is

not stalled.

CBH

01H

RS_FULL_STALL.MEC

MEC RS full.

This event counts the number of cycles the allocation pipe line

stalled due to the RS for the MEC cluster is full.

CBH

1FH

RS_FULL_STALL.ALL

Any RS full.

This event counts the number of cycles that the allocation pipe

line stalled due to any one of the RS is full.

CDH

01H

CYCLES_DIV_BUSY.AN

Y

Divider Busy.

This event counts the number of cycles the divider is busy.

E6H

01H

BACLEARS.ALL

BACLEARS asserted for

any branch.

This event counts the number of baclears for any type of branch.

E6H

08H

BACLEARS.RETURN

BACLEARS asserted for

return branch.

This event counts the number of baclears for return branches.

E6H

10H

BACLEARS.COND

BACLEARS asserted for

conditional branch.

This event counts the number of baclears for conditional

branches.

E7H

01H

MS_DECODED.MS_ENT

RY

MS Decode starts.

This event counts the number of times the MSROM starts a flow

of UOPS.

Table 19-25. Performance Events for Silvermont Microarchitecture

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment