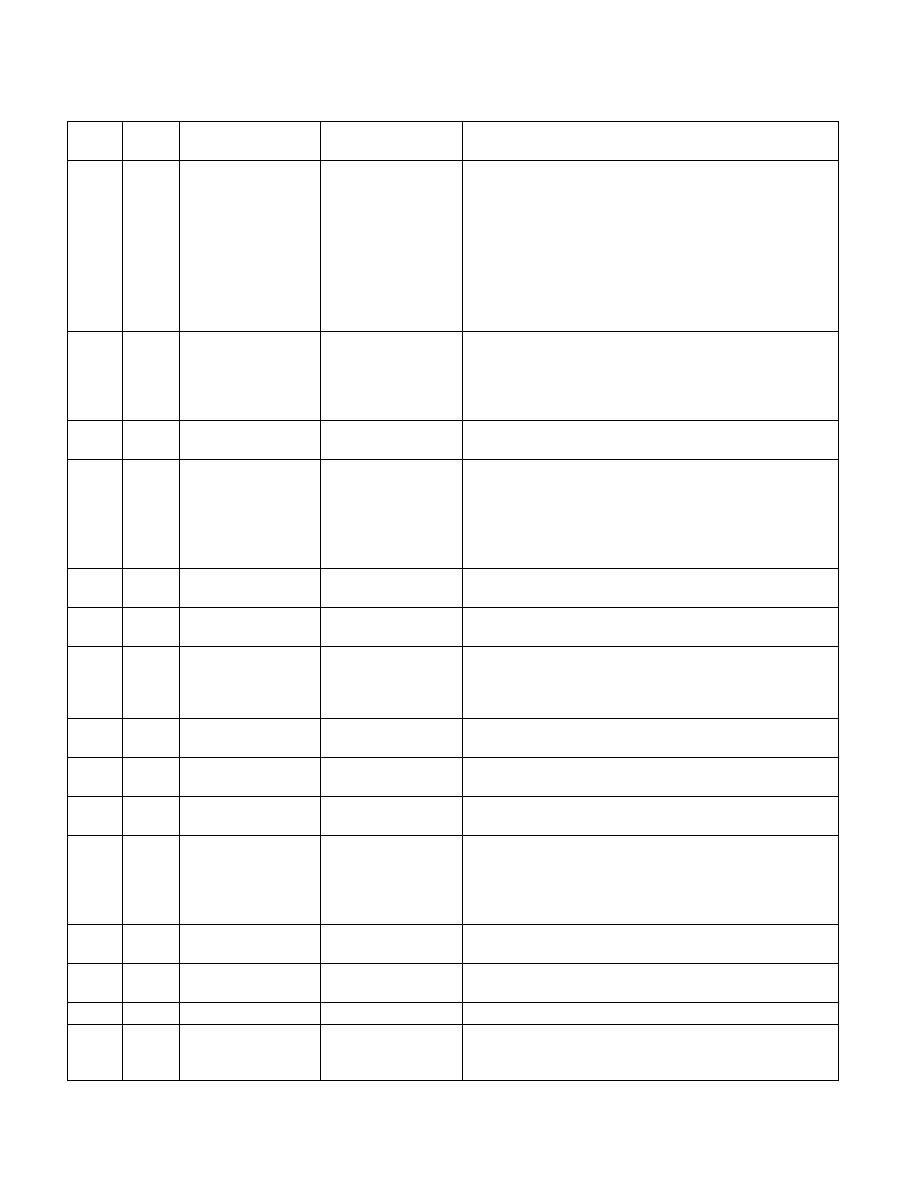

Vol. 3B 19-151

PERFORMANCE-MONITORING EVENTS

31H

00H

CORE_REJECT_L2Q.ALL Counts the number of

request that were not

accepted into the L2Q

because the L2Q is

FULL.

This event counts the number of demand and L1 prefetcher

requests rejected by the L2Q due to a full or nearly full condition

which likely indicates back pressure from L2Q. It also counts

requests that would have gone directly to the XQ, but are

rejected due to a full or nearly full condition, indicating back

pressure from the IDI link. The L2Q may also reject transactions

from a core to insure fairness between cores, or to delay a core's

dirty eviction when the address conflicts incoming external

snoops. (Note that L2 prefetcher requests that are dropped are

not counted by this event.).

3CH

00H

CPU_CLK_UNHALTED.C

ORE_P

Core cycles when core

is not halted.

This event counts the number of core cycles while the core is not

in a halt state. The core enters the halt state when it is running

the HLT instruction. In mobile systems the core frequency may

change from time to time. For this reason this event may have a

changing ratio with regards to time.

N/A

N/A

CPU_CLK_UNHALTED.C

ORE

Instructions retired.

This uses the fixed counter 1 to count the same condition as

CPU_CLK_UNHALTED.CORE_P does.

3CH

01H

CPU_CLK_UNHALTED.R

EF_P

Reference cycles when

core is not halted.

This event counts the number of reference cycles that the core

is not in a halt state. The core enters the halt state when it is

running the HLT instruction.

In mobile systems the core frequency may change from time.

This event is not affected by core frequency changes but counts

as if the core is running at the maximum frequency all the time.

N/A

N/A

CPU_CLK_UNHALTED.R

EF_TSC

Instructions retired.

This uses the fixed counter 2 to count the same condition as

CPU_CLK_UNHALTED.REF_P does.

80H

01H

ICACHE.HIT

Instruction fetches

from Icache.

This event counts all instruction fetches from the instruction

cache.

80H

02H

ICACHE.MISSES

Icache miss.

This event counts all instruction fetches that miss the

Instruction cache or produce memory requests. This includes

uncacheable fetches. An instruction fetch miss is counted only

once and not once for every cycle it is outstanding.

80H

03H

ICACHE.ACCESSES

Instruction fetches.

This event counts all instruction fetches, including uncacheable

fetches.

B7H

01H

OFFCORE_RESPONSE_

0

Requires MSR_OFFCORE_RESP0 to specify request type and

response.

B7H

02H

OFFCORE_RESPONSE_

1

Requires MSR_OFFCORE_RESP1 to specify request type and

response.

C0H

00H

INST_RETIRED.ANY_P Instructions retired

(PEBS supported with

IA32_PMC0).

This event counts the number of instructions that retire

execution. For instructions that consist of multiple micro-ops,

this event counts the retirement of the last micro-op of the

instruction. The counter continues counting during hardware

interrupts, traps, and inside interrupt handlers.

N/A

N/A

INST_RETIRED.ANY

Instructions retired.

This uses the fixed counter 0 to count the same condition as

INST_RETIRED.ANY_P does.

C2H

01H

UOPS_RETIRED.MS

MSROM micro-ops

retired.

This event counts the number of micro-ops retired that were

supplied from MSROM.

C2H

10H

UOPS_RETIRED.ALL

Micro-ops retired.

This event counts the number of micro-ops retired.

C3H

01H

MACHINE_CLEARS.SMC Self-Modifying Code

detected.

This event counts the number of times that a program writes to

a code section. Self-modifying code causes a severe penalty in all

Intel® architecture processors.

Table 19-25. Performance Events for Silvermont Microarchitecture

Event

Num.

Umask

Value

Event Name

Definition

Description and Comment