19-130 Vol. 3B

PERFORMANCE-MONITORING EVENTS

The snoop operation may change the cache line state. If the

other core issued a read request that hit this core in E state,

typically the state changes to S state in this core. If the

other core issued a read for ownership request (due a write

miss or hit to S state) that hits this core's cache line in E or S

state, this typically results in invalidation of the cache line in

this core. If the snoop hits a line in M state, the state is

changed at a later opportunity.

These snoops are performed through the L1 data cache

store port. Therefore, frequent snoops may conflict with

extensive stores to the L1 data cache, which may increase

store latency and impact performance.

7AH

See

BUS_HIT_DRV.

(Bus Agents)

HIT signal asserted.

This event counts the number of bus cycles during which

the processor drives the HIT# pin to signal HIT snoop

response.

7BH

See

BUS_HITM_DRV.

(Bus Agents)

HITM signal asserted.

This event counts the number of bus cycles during which

the processor drives the HITM# pin to signal HITM snoop

response.

7DH

See

BUSQ_EMPTY.

(Core)

Bus queue empty.

This event counts the number of cycles during which the

core did not have any pending transactions in the bus queue.

It also counts when the core is halted and the other core is

not halted.

This event can count occurrences for this core or both cores.

7EH

See

and

SNOOP_STALL_

DRV.(Core and Bus Agents)

Bus stalled for snoops. This event counts the number of times that the bus snoop

stall signal is asserted. To obtain the number of bus cycles

during which snoops on the bus are prohibited, multiply the

event count by two.

During the snoop stall cycles, no new bus transactions

requiring a snoop response can be initiated on the bus. A

bus agent asserts a snoop stall signal if it cannot response

to a snoop request within three bus cycles.

7FH

See

BUS_IO_WAIT.

(Core)

IO requests waiting in

the bus queue.

This event counts the number of core cycles during which IO

requests wait in the bus queue. With the SELF modifier this

event counts IO requests per core.

With the BOTH_CORE modifier, this event increments by one

for any cycle for which there is a request from either core.

80H

00H

L1I_READS

Instruction fetches.

This event counts all instruction fetches, including

uncacheable fetches that bypass the Instruction Fetch Unit

(IFU).

81H

00H

L1I_MISSES

Instruction Fetch Unit

misses.

This event counts all instruction fetches that miss the

Instruction Fetch Unit (IFU) or produce memory requests.

This includes uncacheable fetches.

An instruction fetch miss is counted only once and not once

for every cycle it is outstanding.

82H

02H

ITLB.SMALL_MISS

ITLB small page

misses.

This event counts the number of instruction fetches from

small pages that miss the ITLB.

82H

10H

ITLB.LARGE_MISS

ITLB large page

misses.

This event counts the number of instruction fetches from

large pages that miss the ITLB.

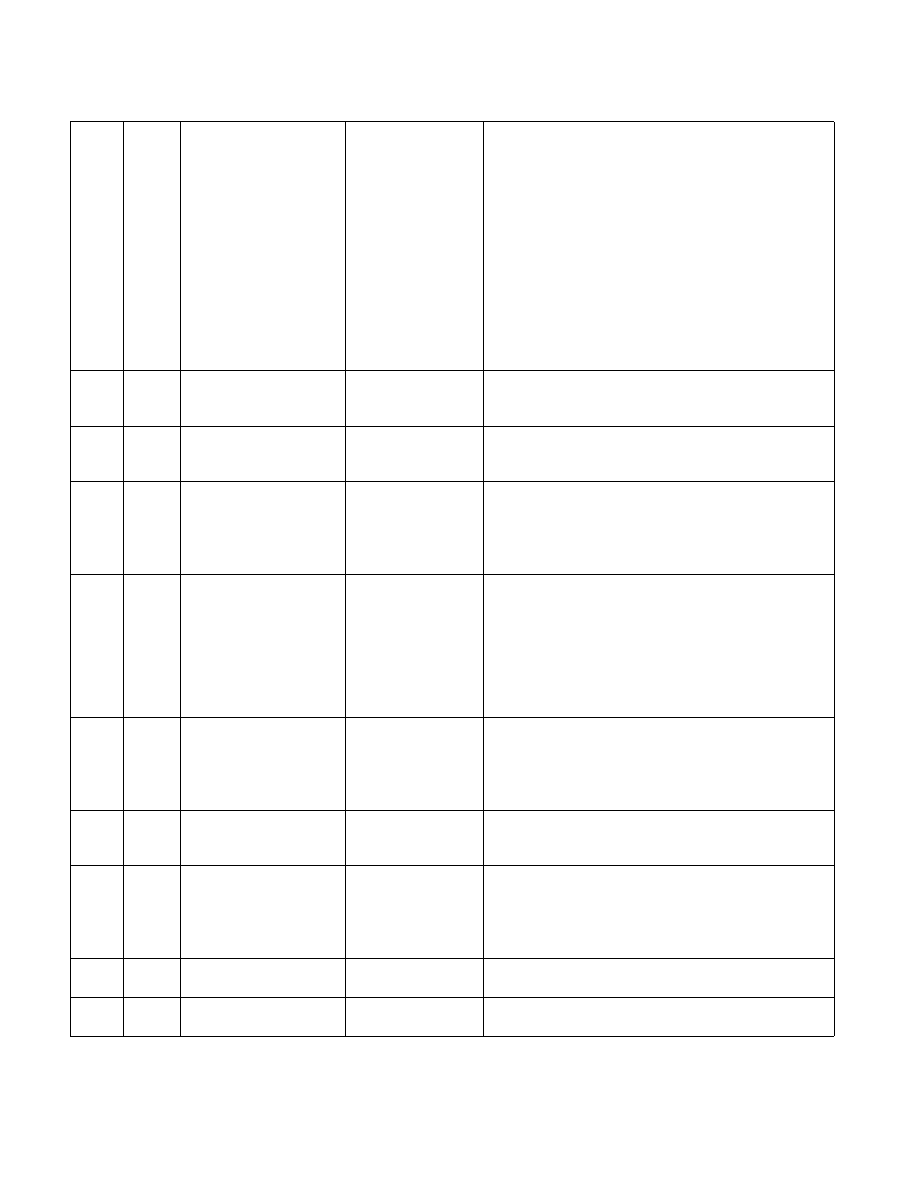

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment