Vol. 3B 19-127

PERFORMANCE-MONITORING EVENTS

4B

H

01

H

SSE_PRE_

MISS.L1

Streaming SIMD

Extensions (SSE)

PrefetchT0

instructions missing all

cache levels.

This event counts the number of times the SSE instructions

prefetchT0 were executed and missed all cache levels.

Due to speculation executed instruction might not retire.

The prefetchT0 instruction prefetches data to the L2 cache

and L1 data cache.

4BH

02H

SSE_PRE_

MISS.L2

Streaming SIMD

Extensions (SSE)

PrefetchT1 and

PrefetchT2

instructions missing all

cache levels.

This event counts the number of times the SSE instructions

prefetchT1 and prefetchT2 were executed and missed all

cache levels.

Due to speculation, an executed instruction might not retire.

The prefetchT1 and PrefetchNT2 instructions prefetch data

to the L2 cache.

4CH

00H

LOAD_HIT_PRE

Load operations

conflicting with a

software prefetch to

the same address.

This event counts load operations sent to the L1 data cache

while a previous Streaming SIMD Extensions (SSE) prefetch

instruction to the same cache line has started prefetching

but has not yet finished.

4EH

10H

L1D_PREFETCH.

REQUESTS

L1 data cache prefetch

requests.

This event counts the number of times the L1 data cache

requested to prefetch a data cache line. Requests can be

rejected when the L2 cache is busy and resubmitted later or

lost.

All requests are counted, including those that are rejected.

60H

See

and

18-3.

BUS_REQUEST_

OUTSTANDING.

(Core and Bus Agents)

Outstanding cacheable

data read bus

requests duration.

This event counts the number of pending full cache line read

transactions on the bus occurring in each cycle. A read

transaction is pending from the cycle it is sent on the bus

until the full cache line is received by the processor.

The event counts only full-line cacheable read requests from

either the L1 data cache or the L2 prefetchers. It does not

count Read for Ownership transactions, instruction byte

fetch transactions, or any other bus transaction.

61H

See

18-3.

BUS_BNR_DRV.

(Bus Agents)

Number of Bus Not

Ready signals

asserted.

This event counts the number of Bus Not Ready (BNR)

signals that the processor asserts on the bus to suspend

additional bus requests by other bus agents.

A bus agent asserts the BNR signal when the number of

data and snoop transactions is close to the maximum that

the bus can handle. To obtain the number of bus cycles

during which the BNR signal is asserted, multiply the event

count by two.

While this signal is asserted, new transactions cannot be

submitted on the bus. As a result, transaction latency may

have higher impact on program performance.

62

H

See

18-3.

BUS_DRDY_

CLOCKS.(Bus Agents)

Bus cycles when data

is sent on the bus.

This event counts the number of bus cycles during which

the DRDY (Data Ready) signal is asserted on the bus. The

DRDY signal is asserted when data is sent on the bus. With

the 'THIS_AGENT' mask this event counts the number of bus

cycles during which this agent (the processor) writes data

on the bus back to memory or to other bus agents. This

includes all explicit and implicit data writebacks, as well as

partial writes.

With the 'ALL_AGENTS' mask, this event counts the number

of bus cycles during which any bus agent sends data on the

bus. This includes all data reads and writes on the bus.

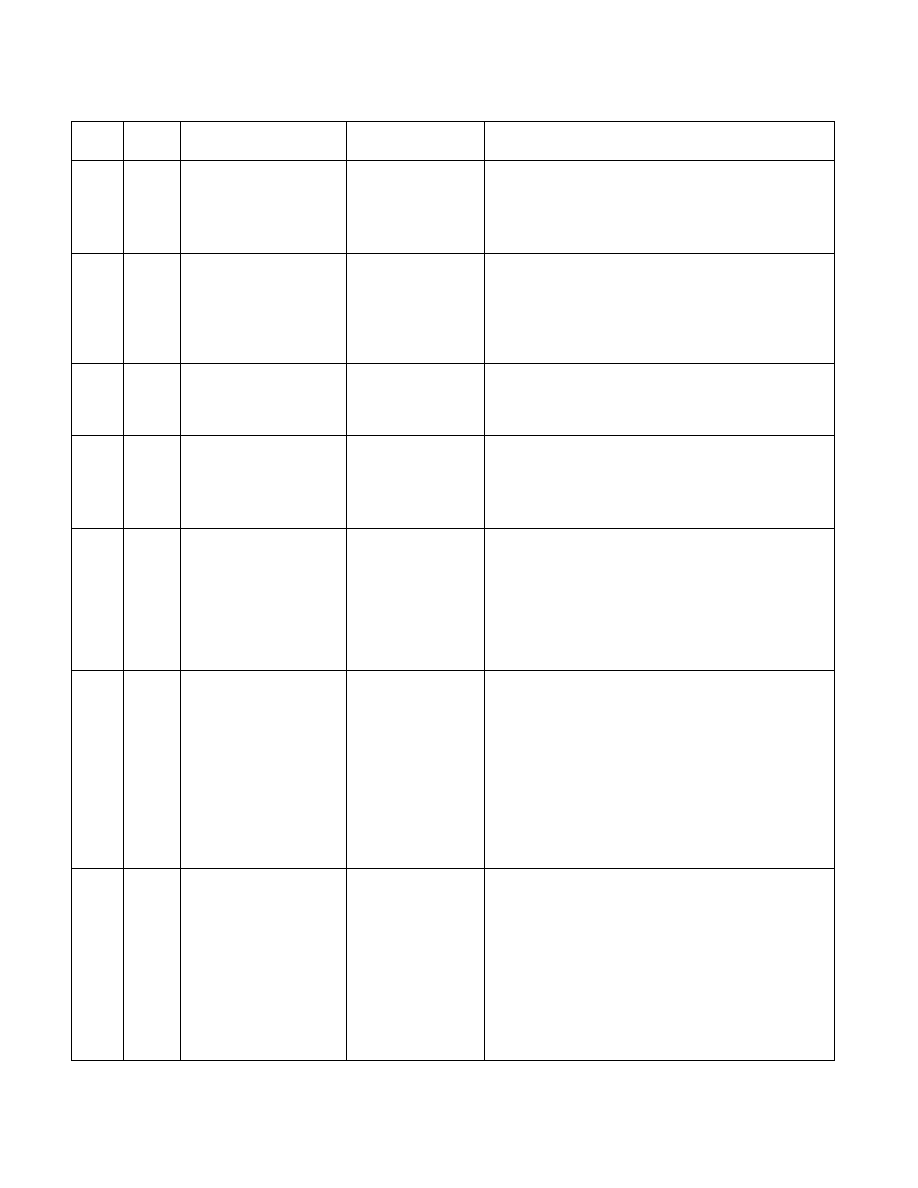

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment