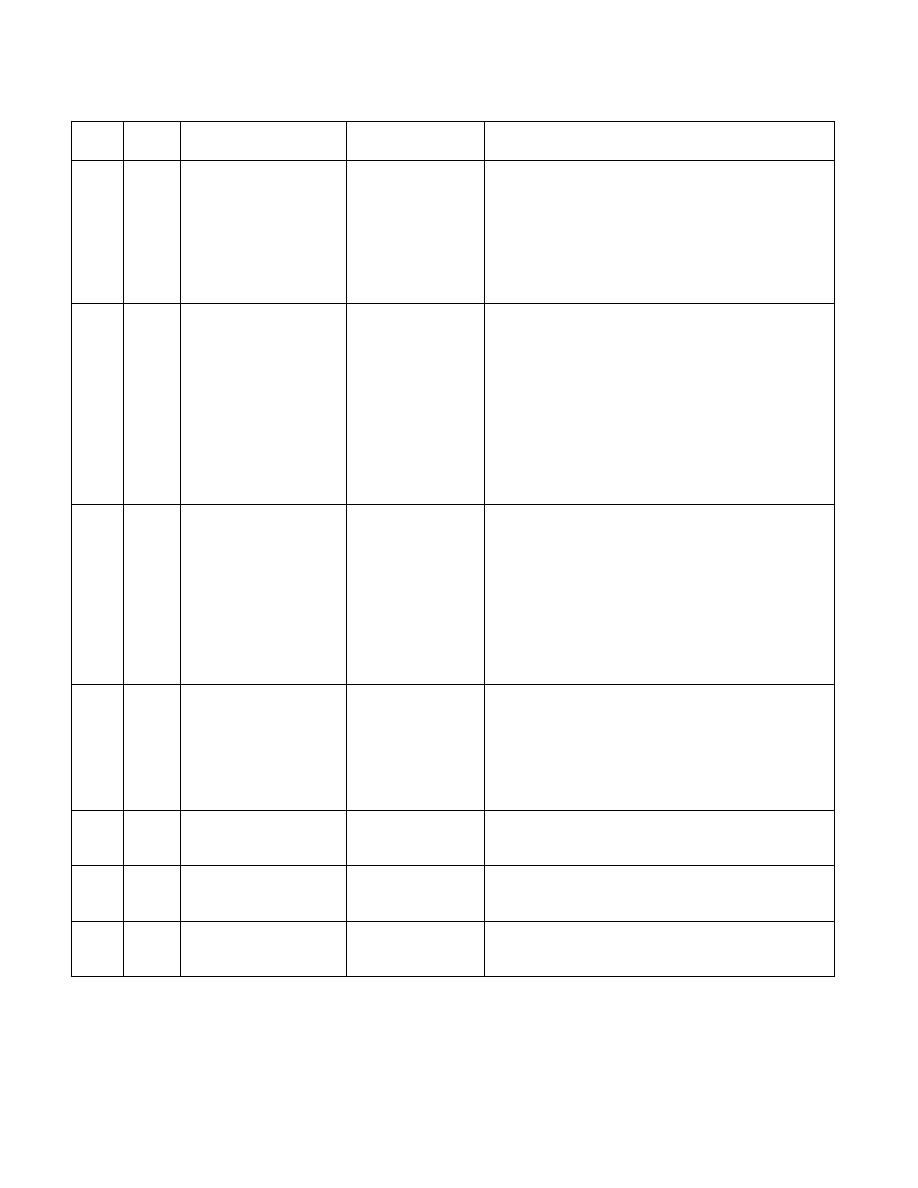

Vol. 3B 19-125

PERFORMANCE-MONITORING EVENTS

3B

H

C0

H

THERMAL_TRIP

Number of thermal

trips.

This event counts the number of thermal trips. A thermal

trip occurs whenever the processor temperature exceeds

the thermal trip threshold temperature.

Following a thermal trip, the processor automatically

reduces frequency and voltage. The processor checks the

temperature every millisecond and returns to normal when

the temperature falls below the thermal trip threshold

temperature.

3C

H

00

H

CPU_CLK_

UNHALTED.

CORE_P

Core cycles when core

is not halted.

This event counts the number of core cycles while the core

is not in a halt state. The core enters the halt state when it

is running the HLT instruction. This event is a component in

many key event ratios.

The core frequency may change due to transitions

associated with Enhanced Intel SpeedStep Technology or

TM2. For this reason, this event may have a changing ratio in

regard to time.

When the core frequency is constant, this event can give

approximate elapsed time while the core not in halt state.

This is an architectural performance event.

3C

H

01

H

CPU_CLK_

UNHALTED.BUS

Bus cycles when core

is not halted.

This event counts the number of bus cycles while the core is

not in the halt state. This event can give a measurement of

the elapsed time while the core was not in the halt state.

The core enters the halt state when it is running the HLT

instruction.

The event also has a constant ratio with

CPU_CLK_UNHALTED.REF event, which is the maximum bus

to processor frequency ratio.

Non-halted bus cycles are a component in many key event

ratios.

3C

H

02

H

CPU_CLK_

UNHALTED.NO

_OTHER

Bus cycles when core

is active and the other

is halted.

This event counts the number of bus cycles during which

the core remains non-halted and the other core on the

processor is halted.

This event can be used to determine the amount of

parallelism exploited by an application or a system. Divide

this event count by the bus frequency to determine the

amount of time that only one core was in use.

40

H

See

L1D_CACHE_LD.

(Cache Line State)

L1 cacheable data

reads.

This event counts the number of data reads from cacheable

memory. Locked reads are not counted.

41

H

See

L1D_CACHE_ST.

(Cache Line State)

L1 cacheable data

writes.

This event counts the number of data writes to cacheable

memory. Locked writes are not counted.

42

H

See

L1D_CACHE_

LOCK.(Cache Line State)

L1 data cacheable

locked reads.

This event counts the number of locked data reads from

cacheable memory.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment