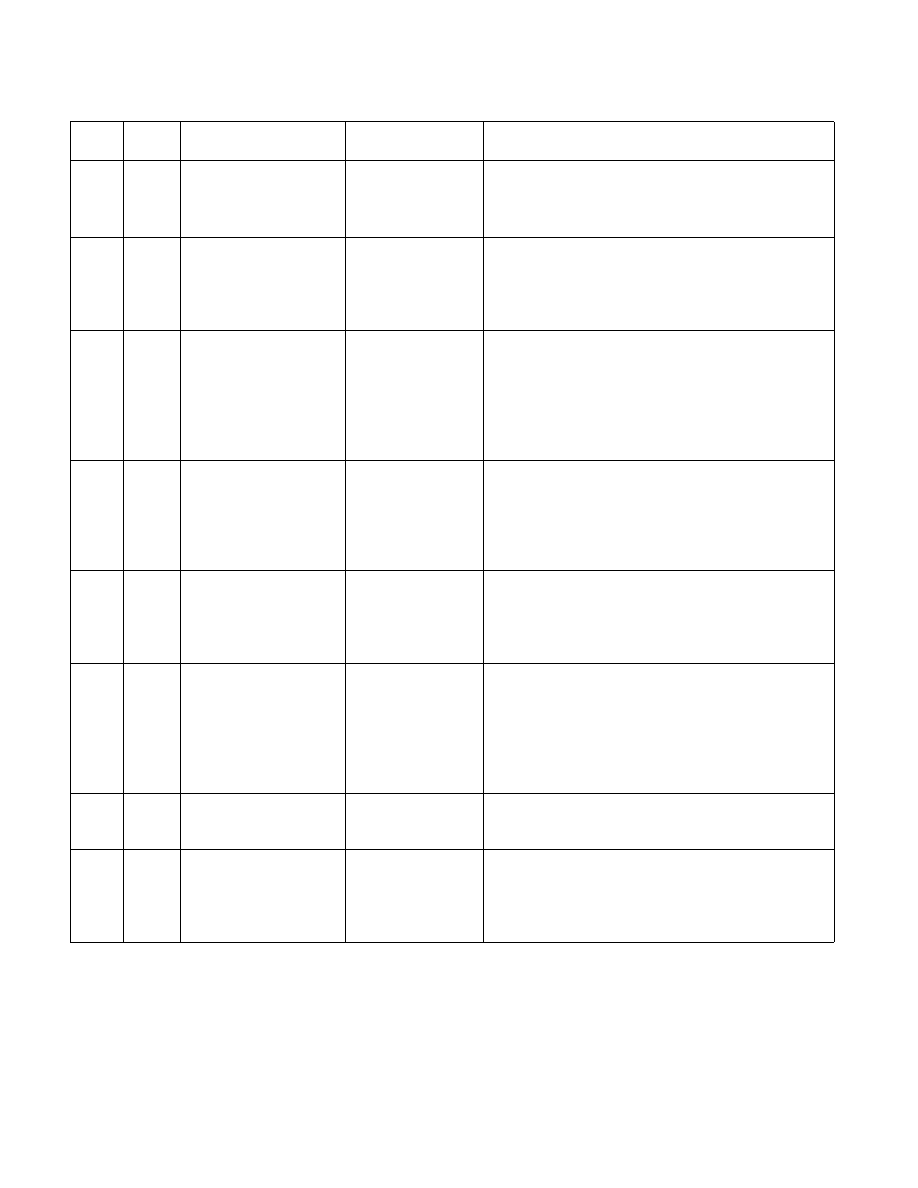

19-122 Vol. 3B

PERFORMANCE-MONITORING EVENTS

13

H

00

H

DIV

Divide operations

executed.

This event counts the number of divide operations

executed. This includes integer divides, floating point

divides and square-root operations executed.

Use IA32_PMC1 only.

14

H

00

H

CYCLES_DIV

_BUSY

Cycles the divider

busy.

This event counts the number of cycles the divider is busy

executing divide or square root operations. The divide can

be integer, X87 or Streaming SIMD Extensions (SSE). The

square root operation can be either X87 or SSE.

Use IA32_PMC0 only.

18

H

00

H

IDLE_DURING

_DIV

Cycles the divider is

busy and all other

execution units are

idle.

This event counts the number of cycles the divider is busy

(with a divide or a square root operation) and no other

execution unit or load operation is in progress.

Load operations are assumed to hit the L1 data cache. This

event considers only micro-ops dispatched after the divider

started operating.

Use IA32_PMC0 only.

19

H

00

H

DELAYED_

BYPASS.FP

Delayed bypass to FP

operation.

This event counts the number of times floating point

operations use data immediately after the data was

generated by a non-floating point execution unit. Such cases

result in one penalty cycle due to data bypass between the

units.

Use IA32_PMC1 only.

19

H

01

H

DELAYED_

BYPASS.SIMD

Delayed bypass to

SIMD operation.

This event counts the number of times SIMD operations use

data immediately after the data was generated by a non-

SIMD execution unit. Such cases result in one penalty cycle

due to data bypass between the units.

Use IA32_PMC1 only.

19

H

02

H

DELAYED_

BYPASS.LOAD

Delayed bypass to

load operation.

This event counts the number of delayed bypass penalty

cycles that a load operation incurred.

When load operations use data immediately after the data

was generated by an integer execution unit, they may

(pending on certain dynamic internal conditions) incur one

penalty cycle due to delayed data bypass between the units.

Use IA32_PMC1 only.

21

H

See

L2_ADS.(Core)

Cycles L2 address bus

is in use.

This event counts the number of cycles the L2 address bus

is being used for accesses to the L2 cache or bus queue. It

can count occurrences for this core or both cores.

23H

See

L2_DBUS_BUSY

_RD.(Core)

Cycles the L2

transfers data to the

core.

This event counts the number of cycles during which the L2

data bus is busy transferring data from the L2 cache to the

core. It counts for all L1 cache misses (data and instruction)

that hit the L2 cache.

This event can count occurrences for this core or both cores.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment