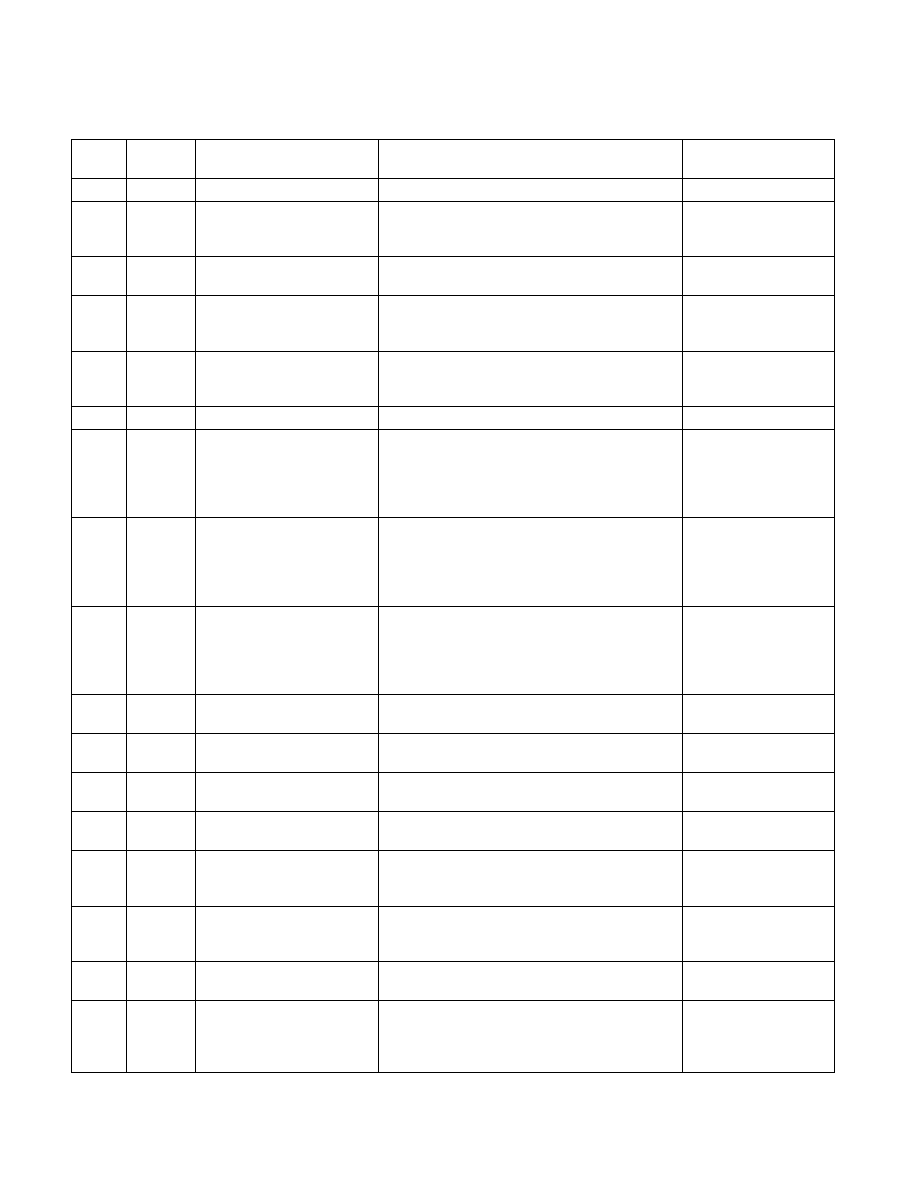

Vol. 3B 19-91

PERFORMANCE-MONITORING EVENTS

27H

F0H

L2_WRITE.LOCK.MESI

Counts all L2 demand lock RFO requests.

28H

01H

L1D_WB_L2.I_STATE

Counts number of L1 writebacks to the L2 where

the cache line to be written is in the I (invalid) state,

i.e., a cache miss.

28H

02H

L1D_WB_L2.S_STATE

Counts number of L1 writebacks to the L2 where

the cache line to be written is in the S state.

28H

04H

L1D_WB_L2.E_STATE

Counts number of L1 writebacks to the L2 where

the cache line to be written is in the E (exclusive)

state.

28H

08H

L1D_WB_L2.M_STATE

Counts number of L1 writebacks to the L2 where

the cache line to be written is in the M (modified)

state.

28H

0FH

L1D_WB_L2.MESI

Counts all L1 writebacks to the L2 .

2EH

41H

L3_LAT_CACHE.MISS

Counts uncore Last Level Cache misses. Because

cache hierarchy, cache sizes and other

implementation-specific characteristics; value

comparison to estimate performance differences is

not recommended.

2EH

4FH

L3_LAT_CACHE.REFERENCE

Counts uncore Last Level Cache references.

Because cache hierarchy, cache sizes and other

implementation-specific characteristics; value

comparison to estimate performance differences is

not recommended.

3CH

00H

CPU_CLK_UNHALTED.THREAD

_P

Counts the number of thread cycles while the

thread is not in a halt state. The thread enters the

halt state when it is running the HLT instruction.

The core frequency may change from time to time

due to power or thermal throttling.

3CH

01H

CPU_CLK_UNHALTED.REF_P

Increments at the frequency of TSC when not

halted.

49H

01H

DTLB_MISSES.ANY

Counts the number of misses in the STLB which

causes a page walk.

49H

02H

DTLB_MISSES.WALK_COMPLE

TED

Counts number of misses in the STLB which

resulted in a completed page walk.

49H

04H

DTLB_MISSES.WALK_CYCLES

Counts cycles of page walk due to misses in the

STLB.

49H

10H

DTLB_MISSES.STLB_HIT

Counts the number of DTLB first level misses that

hit in the second level TLB. This event is only

relevant if the core contains multiple DTLB levels.

49H

20H

DTLB_MISSES.PDE_MISS

Number of DTLB misses caused by low part of

address, includes references to 2M pages because

2M pages do not use the PDE.

49H

80H

DTLB_MISSES.LARGE_WALK_C

OMPLETED

Counts number of completed large page walks due

to misses in the STLB.

4CH

01H

LOAD_HIT_PRE

Counts load operations sent to the L1 data cache

while a previous SSE prefetch instruction to the

same cache line has started prefetching but has not

yet finished.

Counter 0, 1 only.

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment