Vol. 3A 2-21

SYSTEM ARCHITECTURE OVERVIEW

ating-system or executive procedures (that is, procedures running at privilege level 0). Others can be executed at

any privilege level and are thus available to application programs.

Table 2-3 lists the system instructions and indicates whether they are available and useful for application

programs. These instructions are described in the Intel® 64 and IA-32 Architectures Software Developer’s Manual,

Volumes 2A, 2B, 2C & 2D.

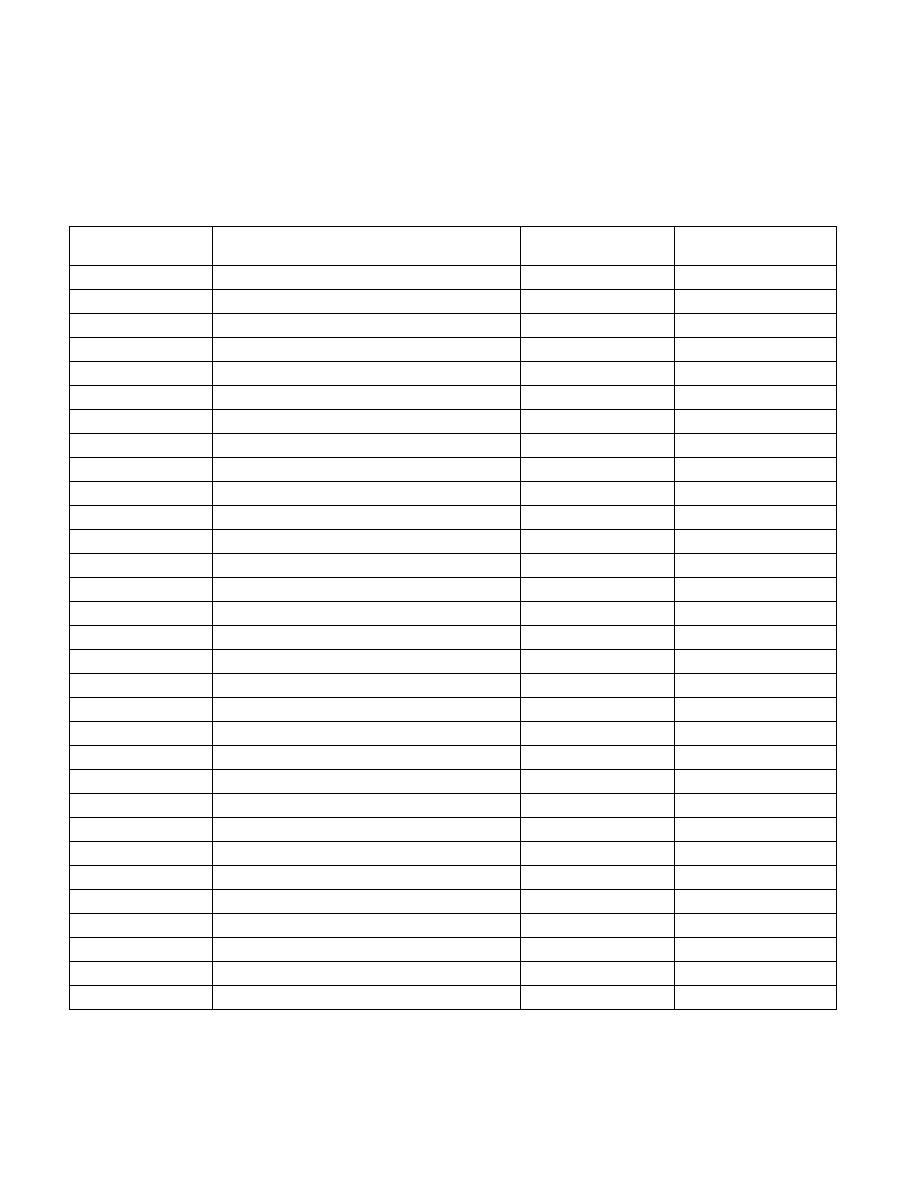

Table 2-3. Summary of System Instructions

Instruction

Description

Useful to

Application?

Protected from

Application?

LLDT

Load LDT Register

No

Yes

SLDT

Store LDT Register

No

If CR4.UMIP = 1

LGDT

Load GDT Register

No

Yes

SGDT

Store GDT Register

No

If CR4.UMIP = 1

LTR

Load Task Register

No

Yes

STR

Store Task Register

No

If CR4.UMIP = 1

LIDT

Load IDT Register

No

Yes

SIDT

Store IDT Register

No

If CR4.UMIP = 1

MOV CRn

Load and store control registers

No

Yes

SMSW

Store MSW

Yes

If CR4.UMIP = 1

LMSW

Load MSW

No

Yes

CLTS

Clear TS flag in CR0

No

Yes

ARPL

Adjust RPL

Yes

1, 5

No

LAR

Load Access Rights

Yes

No

LSL

Load Segment Limit

Yes

No

VERR

Verify for Reading

Yes

No

VERW

Verify for Writing

Yes

No

MOV DRn

Load and store debug registers

No

Yes

INVD

Invalidate cache, no writeback

No

Yes

WBINVD

Invalidate cache, with writeback

No

Yes

INVLPG

Invalidate TLB entry

No

Yes

HLT

Halt Processor

No

Yes

LOCK (Prefix)

Bus Lock

Yes

No

RSM

Return from system management mode

No

Yes

RDMSR

3

Read Model-Specific Registers

No

Yes

WRMSR

3

Write Model-Specific Registers

No

Yes

RDPMC

4

Read Performance-Monitoring Counter

Yes

Yes

2

RDTSC

3

Read Time-Stamp Counter

Yes

Yes

2

RDTSCP

7

Read Serialized Time-Stamp Counter

Yes

Yes

2

XGETBV

Return the state of XCR0

Yes

No

XSETBV

Enable one or more processor extended states

No

6

Yes