2-20 Vol. 3A

SYSTEM ARCHITECTURE OVERVIEW

•

XCR0.BNDCSR (bit 4): If 1, MPX instructions can be executed and the XSAVE feature set can be used to

manage the BNDCFGU and BNDSTATUS registers.

•

XCR0.opmask (bit 5): If 1, AVX-512 instructions can be executed and the XSAVE feature set can be used to

manage the opmask registers k0–k7.

•

XCR0.ZMM_Hi256 (bit 6): If 1, AVX-512 instructions can be executed and the XSAVE feature set can be used to

manage the upper halves of the lower ZMM registers (ZMM0-ZMM15 in 64-bit mode; otherwise ZMM0-ZMM7).

•

XCR0.Hi16_ZMM (bit 7): If 1, AVX-512 instructions can be executed and the XSAVE feature set can be used to

manage the upper ZMM registers (ZMM16-ZMM31, only in 64-bit mode).

•

XCR0.PKRU (bit 9): If 1, the XSAVE feature set can be used to manage the PKRU register (see Section 2.7).

An attempt to use XSETBV to write to XCR0 results in general-protection exceptions (#GP) if it would do any of the

following:

•

Set a bit reserved in XCR0 for a given processor (as determined by the contents of EAX and EDX after executing

CPUID with EAX=0DH, ECX= 0H).

•

Clear XCR0.x87.

•

Clear XCR0.SSE and set XCR0.AVX.

•

Clear XCR0.AVX and set any of XCR0.opmask, XCR0.ZMM_Hi256, and XCR0.Hi16_ZMM.

•

Set either XCR0.BNDREG and XCR0.BNDCSR while not setting the other.

•

Set any of XCR0.opmask, XCR0.ZMM_Hi256, and XCR0.Hi16_ZMM while not setting all of them.

After reset, all bits (except bit 0) in XCR0 are cleared to zero; XCR0[0] is set to 1.

2.7

PROTECTION KEY RIGHTS REGISTER (PKRU)

If CPUID.(EAX=07H,ECX=0H):ECX.PKU [bit 3] = 1, the processor supports the protection-key feature for IA-32e

paging. The feature allows selective protection of user-mode pages depending on the 4-bit protection key assigned

to each page. The protection key rights register for user pages (PKRU) allows software to specify the access

rights for each protection key.

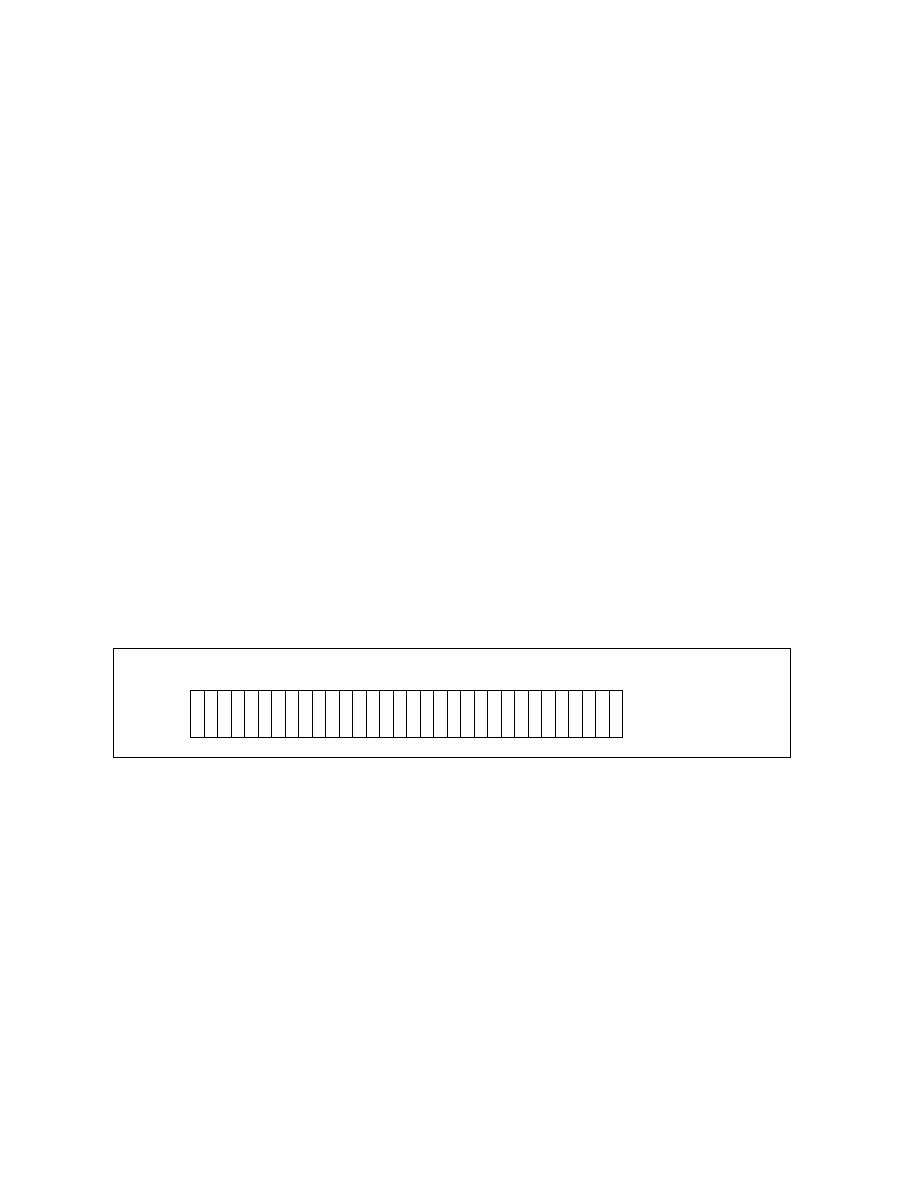

The layout of the PKRU register is shown in Figure 2-9. It contains 16 pairs of disable controls to prevent data

accesses to user-mode linear addresses based on their protection keys. Each protection key i is associated with two

bits in the PKRU register:

•

Bit 2i, shown as “ADi” (access disable): if set, the processor prevents any data accesses to user-mode linear

addresses with protection key i.

•

Bit 2i+1, shown as “WDi” (write disable): if set, the processor prevents write accesses to user-mode linear

addresses with protection key i.

See Section 4.6.2, “Protection Keys,” for details of how the processor uses the PKRU register to control accesses to

user-mode linear addresses.

2.8 SYSTEM

INSTRUCTION

SUMMARY

System instructions handle system-level functions such as loading system registers, managing the cache,

managing interrupts, or setting up the debug registers. Many of these instructions can be executed only by oper-

Figure 2-9. Protection Key Rights Register for User Pages (PKRU)

A

31

9

8

7

6

5

4

3

2

1

0

14

18 17

20

16 15

22 21

19

30 29 28 27

25 24 23

26

Bit Position

10

11

12

13

D

W

D

0

A

D

1

W

D

1

0

A

D

W

D

2

A

D

3

W

D

3

2

A

D

W

D

4

A

D

5

W

D

5

4

A

D

W

D

6

A

D

7

W

D

7

6

A

D

W

D

8

A

D

9

W

D

9

8

A

D

W

D

10

A

D

11

W

D

11

10

A

D

W

D

12

A

D

13

W

D

13

12

A

D

W

D

14

A

D

15

W

D

14

15