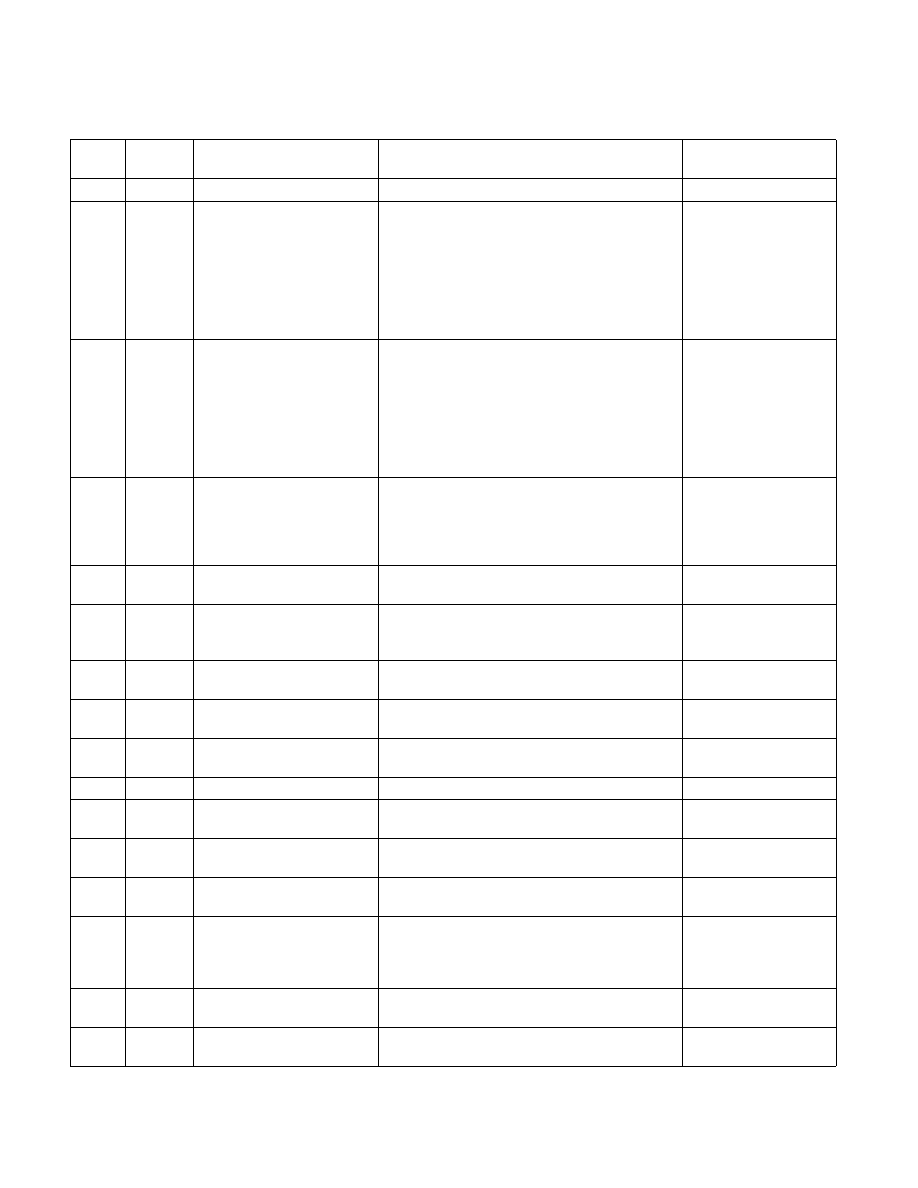

Vol. 3B 19-63

PERFORMANCE-MONITORING EVENTS

28H

0FH

L1D_WB_L2.MESI

Counts all L1 writebacks to the L2 .

2EH

4FH

L3_LAT_CACHE.REFERENCE

This event counts requests originating from the

core that reference a cache line in the last level

cache. The event count includes speculative traffic

but excludes cache line fills due to a L2 hardware-

prefetch. Because cache hierarchy, cache sizes and

other implementation-specific characteristics; value

comparison to estimate performance differences is

not recommended.

2EH

41H

L3_LAT_CACHE.MISS

This event counts each cache miss condition for

references to the last level cache. The event count

may include speculative traffic but excludes cache

line fills due to L2 hardware-prefetches. Because

cache hierarchy, cache sizes and other

implementation-specific characteristics; value

comparison to estimate performance differences is

not recommended.

3CH

00H

CPU_CLK_UNHALTED.THREAD

_P

Counts the number of thread cycles while the

thread is not in a halt state. The thread enters the

halt state when it is running the HLT instruction.

The core frequency may change from time to time

due to power or thermal throttling.

3CH

01H

CPU_CLK_UNHALTED.REF_P

Increments at the frequency of TSC when not

halted.

40H

01H

L1D_CACHE_LD.I_STATE

Counts L1 data cache read requests where the

cache line to be loaded is in the I (invalid) state, i.e.

the read request missed the cache.

Counter 0, 1 only.

40H

02H

L1D_CACHE_LD.S_STATE

Counts L1 data cache read requests where the

cache line to be loaded is in the S (shared) state.

Counter 0, 1 only.

40H

04H

L1D_CACHE_LD.E_STATE

Counts L1 data cache read requests where the

cache line to be loaded is in the E (exclusive) state.

Counter 0, 1 only.

40H

08H

L1D_CACHE_LD.M_STATE

Counts L1 data cache read requests where the

cache line to be loaded is in the M (modified) state.

Counter 0, 1 only.

40H

0FH

L1D_CACHE_LD.MESI

Counts L1 data cache read requests.

Counter 0, 1 only.

41H

02H

L1D_CACHE_ST.S_STATE

Counts L1 data cache store RFO requests where the

cache line to be loaded is in the S (shared) state.

Counter 0, 1 only.

41H

04H

L1D_CACHE_ST.E_STATE

Counts L1 data cache store RFO requests where the

cache line to be loaded is in the E (exclusive) state.

Counter 0, 1 only.

41H

08H

L1D_CACHE_ST.M_STATE

Counts L1 data cache store RFO requests where

cache line to be loaded is in the M (modified) state.

Counter 0, 1 only.

42H

01H

L1D_CACHE_LOCK.HIT

Counts retired load locks that hit in the L1 data

cache or hit in an already allocated fill buffer. The

lock portion of the load lock transaction must hit in

the L1D.

The initial load will pull

the lock into the L1 data

cache. Counter 0, 1 only.

42H

02H

L1D_CACHE_LOCK.S_STATE

Counts L1 data cache retired load locks that hit the

target cache line in the shared state.

Counter 0, 1 only.

42H

04H

L1D_CACHE_LOCK.E_STATE

Counts L1 data cache retired load locks that hit the

target cache line in the exclusive state.

Counter 0, 1 only.

Table 19-17. Non-Architectural Performance Events In the Processor Core for

Intel® Core™ i7 Processor and Intel® Xeon® Processor 5500 Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment