19-54 Vol. 3B

PERFORMANCE-MONITORING EVENTS

Non-architecture performance monitoring events in the processor core that are applicable only to Intel Xeon

processor E5 family (and Intel Core i7-3930 processor) based on Intel microarchitecture code name Sandy Bridge,

with CPUID signature of DisplayFamily_DisplayModel 06_2DH, are listed in Table 19-15.

OFFCORE_RESPONSE.DEMAND_RFO.LLC_HIT.NO_SNOOP_NEEDED_N

1003C0002H

OFFCORE_RESPONSE.DEMAND_RFO.LLC_HIT.SNOOP_MISS_N

2003C0002H

OFFCORE_RESPONSE.DEMAND_RFO.LLC_MISS.DRAM_N

300400002H

OFFCORE_RESPONSE.OTHER.ANY_RESPONSE_N

18000H

OFFCORE_RESPONSE.PF_L2_CODE_RD.LLC_HIT.HIT_OTHER_CORE_NO_FWD_N

4003C0040H

OFFCORE_RESPONSE.PF_L2_CODE_RD.LLC_HIT.HITM_OTHER_CORE_N

10003C0040H

OFFCORE_RESPONSE.PF_L2_CODE_RD.LLC_HIT.NO_SNOOP_NEEDED_N

1003C0040H

OFFCORE_RESPONSE.PF_L2_CODE_RD.LLC_HIT.SNOOP_MISS_N

2003C0040H

OFFCORE_RESPONSE.PF_L2_CODE_RD.LLC_MISS.DRAM_N

300400040H

OFFCORE_RESPONSE.PF_L2_DATA_RD.LLC_MISS.DRAM_N

300400010H

OFFCORE_RESPONSE.PF_L2_RFO.LLC_HIT.ANY_RESPONSE_N

3F803C0020H

OFFCORE_RESPONSE.PF_L2_RFO.LLC_HIT.HIT_OTHER_CORE_NO_FWD_N

4003C0020H

OFFCORE_RESPONSE.PF_L2_RFO.LLC_HIT.HITM_OTHER_CORE_N

10003C0020H

OFFCORE_RESPONSE.PF_L2_RFO.LLC_HIT.NO_SNOOP_NEEDED_N

1003C0020H

OFFCORE_RESPONSE.PF_L2_RFO.LLC_HIT.SNOOP_MISS_N

2003C0020H

OFFCORE_RESPONSE.PF_L2_RFO.LLC_MISS.DRAM_N

300400020H

OFFCORE_RESPONSE.PF_LLC_CODE_RD.LLC_HIT.HIT_OTHER_CORE_NO_FWD_N

4003C0200H

OFFCORE_RESPONSE.PF_LLC_CODE_RD.LLC_HIT.HITM_OTHER_CORE_N

10003C0200H

OFFCORE_RESPONSE.PF_LLC_CODE_RD.LLC_HIT.NO_SNOOP_NEEDED_N

1003C0200H

OFFCORE_RESPONSE.PF_LLC_CODE_RD.LLC_HIT.SNOOP_MISS_N

2003C0200H

OFFCORE_RESPONSE.PF_LLC_CODE_RD.LLC_MISS.DRAM_N

300400200H

OFFCORE_RESPONSE.PF_LLC_DATA_RD.LLC_MISS.DRAM_N

300400080H

OFFCORE_RESPONSE.PF_LLC_RFO.LLC_HIT.ANY_RESPONSE_N

3F803C0100H

OFFCORE_RESPONSE.PF_LLC_RFO.LLC_HIT.HIT_OTHER_CORE_NO_FWD_N

4003C0100H

OFFCORE_RESPONSE.PF_LLC_RFO.LLC_HIT.HITM_OTHER_CORE_N

10003C0100H

OFFCORE_RESPONSE.PF_LLC_RFO.LLC_HIT.NO_SNOOP_NEEDED_N

1003C0100H

OFFCORE_RESPONSE.PF_LLC_RFO.LLC_HIT.SNOOP_MISS_N

2003C0100H

OFFCORE_RESPONSE.PF_LLC_RFO.LLC_MISS.DRAM_N

300400100H

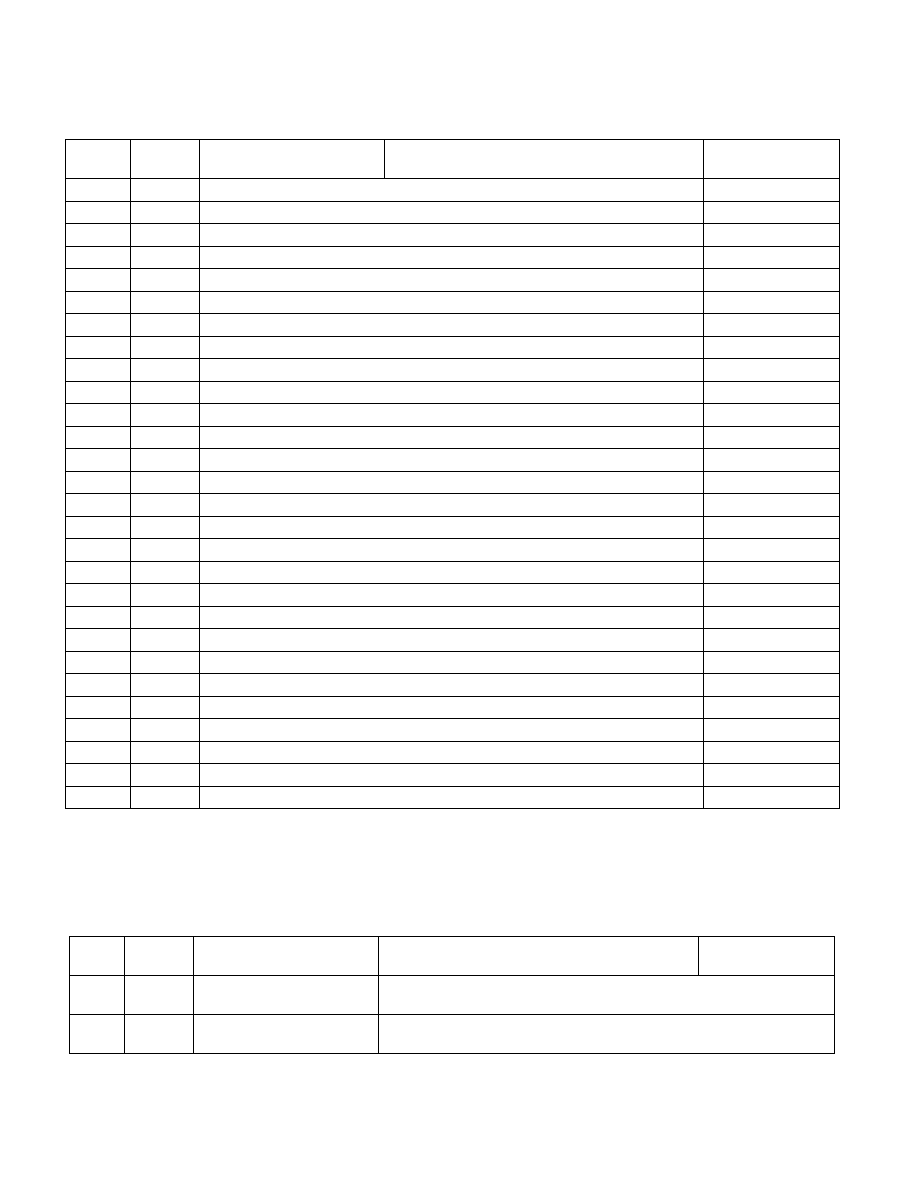

Table 19-15. Non-Architectural Performance Events Applicable only to the Processor Core of

Intel® Xeon® Processor E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

CDH

01H

MEM_TRANS_RETIRED.LOAD_

LATENCY

Additional Configuration: Disable BL bypass and direct2core, and if the memory

is remotely homed. The count is not reliable If the memory is locally homed.

D1H

04H

MEM_LOAD_UOPS_RETIRED.LL

C_HIT

Additional Configuration: Disable BL bypass. Supports PEBS.

Table 19-14. Non-Architectural Performance Events applicable only to the Processor core for 2nd Generation Intel®

Core™ i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment