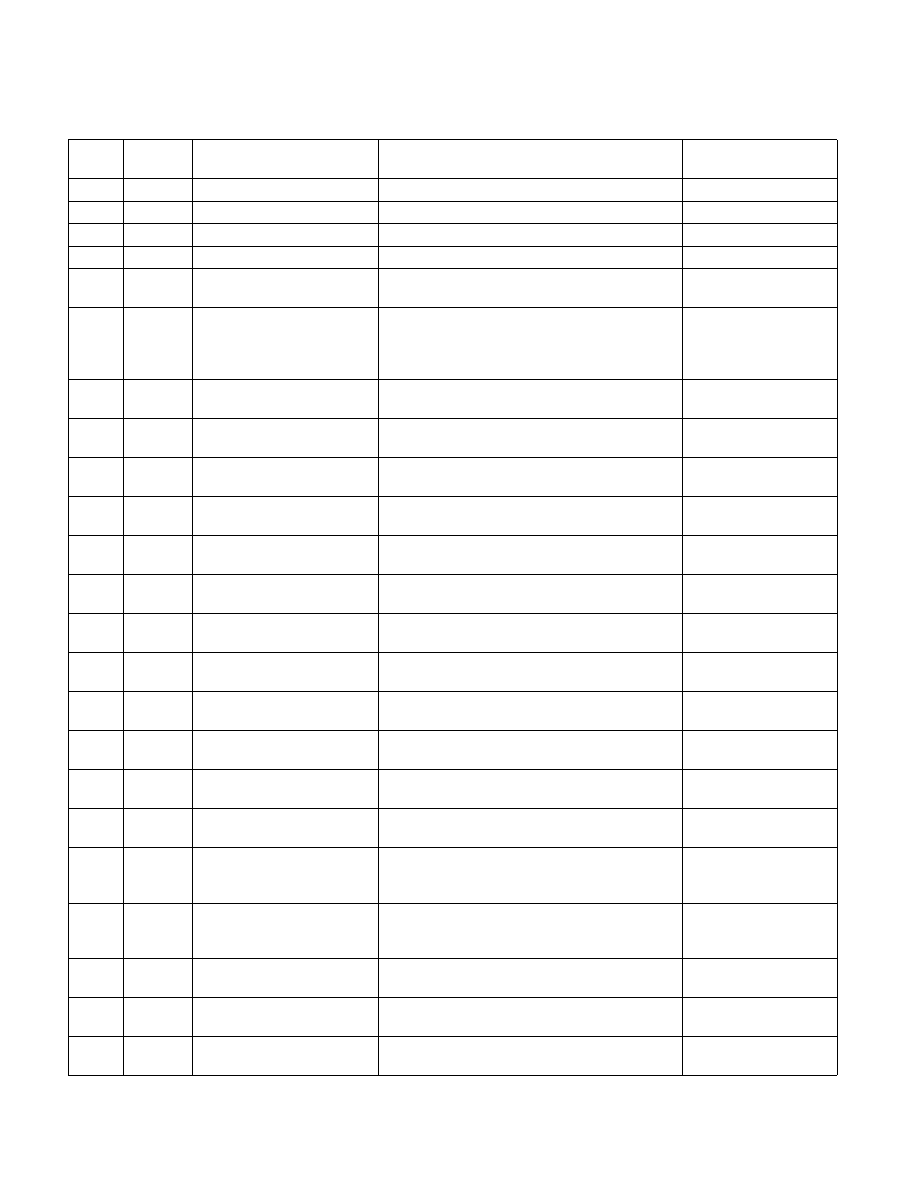

Vol. 3B 19-51

PERFORMANCE-MONITORING EVENTS

CAH

04H

FP_ASSIST.X87_INPUT

Number of X87 assists due to input value.

CAH

08H

FP_ASSIST.SIMD_OUTPUT

Number of SIMD FP assists due to output values.

CAH

10H

FP_ASSIST.SIMD_INPUT

Number of SIMD FP assists due to input values.

CAH

1EH

FP_ASSIST.ANY

Cycles with any input/output SSE* or FP assists.

CCH

20H

ROB_MISC_EVENTS.LBR_INSE

RTS

Count cases of saving new LBR records by

hardware.

CDH

01H

MEM_TRANS_RETIRED.LOAD_

LATENCY

Randomly sampled loads whose latency is above a

user defined threshold. A small fraction of the

overall loads are sampled due to randomization.

PMC3 only.

Specify threshold in MSR

3F6H.

CDH

02H

MEM_TRANS_RETIRED.PRECIS

E_STORE

Sample stores and collect precise store operation

via PEBS record. PMC3 only.

D0H

11H

MEM_UOPS_RETIRED.STLB_MI

SS_LOADS

Retired load uops that miss the STLB.

Supports PEBS. PMC0-3

only regardless HTT.

D0H

12H

MEM_UOPS_RETIRED.STLB_MI

SS_STORES

Retired store uops that miss the STLB.

Supports PEBS. PMC0-3

only regardless HTT.

D0H

21H

MEM_UOPS_RETIRED.LOCK_LO

ADS

Retired load uops with locked access.

Supports PEBS. PMC0-3

only regardless HTT.

D0H

41H

MEM_UOPS_RETIRED.SPLIT_L

OADS

Retired load uops that split across a cacheline

boundary.

Supports PEBS. PMC0-3

only regardless HTT.

D0H

42H

MEM_UOPS_RETIRED.SPLIT_S

TORES

Retired store uops that split across a cacheline

boundary.

Supports PEBS. PMC0-3

only regardless HTT.

D0H

81H

MEM_UOPS_RETIRED.ALL_LOA

DS

All retired load uops.

Supports PEBS. PMC0-3

only regardless HTT.

D0H

82H

MEM_UOPS_RETIRED.ALL_STO

RES

All retired store uops.

Supports PEBS. PMC0-3

only regardless HTT.

D1H

01H

MEM_LOAD_UOPS_RETIRED.L

1_HIT

Retired load uops with L1 cache hits as data

sources.

Supports PEBS. PMC0-3

only regardless HTT.

D1H

02H

MEM_LOAD_UOPS_RETIRED.L

2_HIT

Retired load uops with L2 cache hits as data

sources.

Supports PEBS.

D1H

04H

MEM_LOAD_UOPS_RETIRED.LL

C_HIT

Retired load uops which data sources were data hits

in LLC without snoops required.

Supports PEBS.

D1H

20H

MEM_LOAD_UOPS_RETIRED.LL

C_MISS

Retired load uops which data sources were data

missed LLC (excluding unknown data source).

Supports PEBS.

D1H

40H

MEM_LOAD_UOPS_RETIRED.HI

T_LFB

Retired load uops which data sources were load

uops missed L1 but hit FB due to preceding miss to

the same cache line with data not ready.

Supports PEBS.

D2H

01H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_MISS

Retired load uops whose data source was an on-

package core cache LLC hit and cross-core snoop

missed.

Supports PEBS.

D2H

02H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_HIT

Retired load uops whose data source was an on-

package LLC hit and cross-core snoop hits.

Supports PEBS.

D2H

04H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_HITM

Retired load uops whose data source was an on-

package core cache with HitM responses.

Supports PEBS.

D2H

08H

MEM_LOAD_UOPS_LLC_HIT_R

ETIRED.XSNP_NONE

Retired load uops whose data source was LLC hit

with no snoop required.

Supports PEBS.

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment