19-50 Vol. 3B

PERFORMANCE-MONITORING EVENTS

C1H

08H

OTHER_ASSISTS.AVX_STORE

Number of assists associated with 256-bit AVX

store operations.

C1H

10H

OTHER_ASSISTS.AVX_TO_SSE Number of transitions from AVX-256 to legacy SSE

when penalty applicable.

C1H

20H

OTHER_ASSISTS.SSE_TO_AVX Number of transitions from SSE to AVX-256 when

penalty applicable.

C2H

01H

UOPS_RETIRED.ALL

Counts the number of micro-ops retired, Use

cmask=1 and invert to count active cycles or stalled

cycles.

Supports PEBS.

C2H

02H

UOPS_RETIRED.RETIRE_SLOTS Counts the number of retirement slots used each

cycle.

Supports PEBS.

C3H

02H

MACHINE_CLEARS.MEMORY_O

RDERING

Counts the number of machine clears due to

memory order conflicts.

C3H

04H

MACHINE_CLEARS.SMC

Counts the number of times that a program writes

to a code section.

C3H

20H

MACHINE_CLEARS.MASKMOV

Counts the number of executed AVX masked load

operations that refer to an illegal address range

with the mask bits set to 0.

C4H

00H

BR_INST_RETIRED.ALL_BRAN

CHES

Branch instructions at retirement.

See Table 19-1.

C4H

01H

BR_INST_RETIRED.CONDITION

AL

Counts the number of conditional branch

instructions retired.

Supports PEBS.

C4H

02H

BR_INST_RETIRED.NEAR_CALL Direct and indirect near call instructions retired.

Supports PEBS.

C4H

04H

BR_INST_RETIRED.ALL_BRAN

CHES

Counts the number of branch instructions retired.

Supports PEBS.

C4H

08H

BR_INST_RETIRED.NEAR_RET

URN

Counts the number of near return instructions

retired.

Supports PEBS.

C4H

10H

BR_INST_RETIRED.NOT_TAKE

N

Counts the number of not taken branch instructions

retired.

C4H

20H

BR_INST_RETIRED.NEAR_TAK

EN

Number of near taken branches retired.

Supports PEBS.

C4H

40H

BR_INST_RETIRED.FAR_BRAN

CH

Number of far branches retired.

C5H

00H

BR_MISP_RETIRED.ALL_BRAN

CHES

Mispredicted branch instructions at retirement.

See Table 19-1.

C5H

01H

BR_MISP_RETIRED.CONDITION

AL

Mispredicted conditional branch instructions retired. Supports PEBS.

C5H

02H

BR_MISP_RETIRED.NEAR_CAL

L

Direct and indirect mispredicted near call

instructions retired.

Supports PEBS.

C5H

04H

BR_MISP_RETIRED.ALL_BRAN

CHES

Mispredicted macro branch instructions retired.

Supports PEBS.

C5H

10H

BR_MISP_RETIRED.NOT_TAKE

N

Mispredicted not taken branch instructions retired.

Supports PEBS.

C5H

20H

BR_MISP_RETIRED.TAKEN

Mispredicted taken branch instructions retired.

Supports PEBS.

CAH

02H

FP_ASSIST.X87_OUTPUT

Number of X87 assists due to output value.

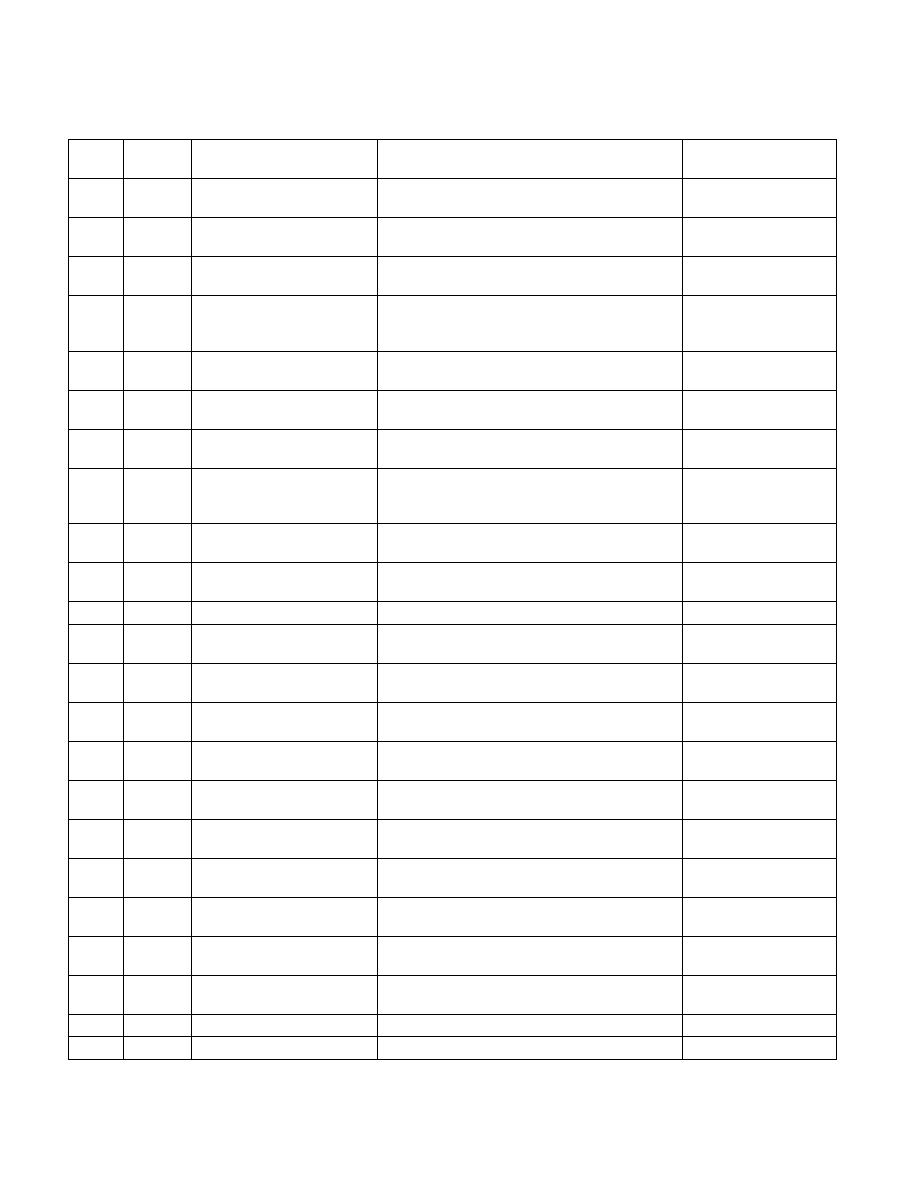

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment