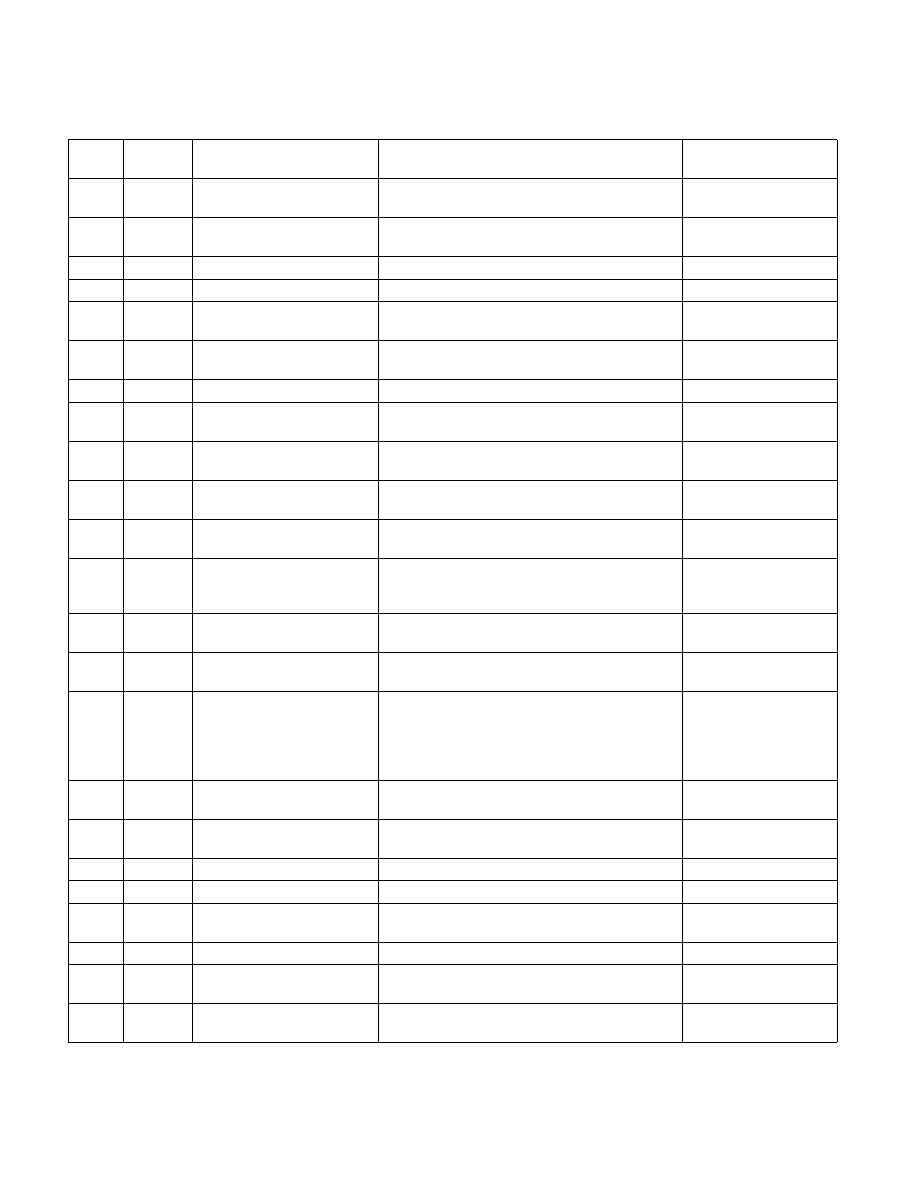

Vol. 3B 19-49

PERFORMANCE-MONITORING EVENTS

A3H

05H

CYCLE_ACTIVITY.STALL_CYCLE

S_L2_PENDING

PMC0-3 only.

A3H

06H

CYCLE_ACTIVITY.STALL_CYCLE

S_L1D_PENDING

PMC2 only.

A8H

01H

LSD.UOPS

Number of Uops delivered by the LSD.

ABH

01H

DSB2MITE_SWITCHES.COUNT

Number of DSB to MITE switches.

ABH

02H

DSB2MITE_SWITCHES.PENALT

Y_CYCLES

Cycles DSB to MITE switches caused delay.

ACH

02H

DSB_FILL.OTHER_CANCEL

Cases of cancelling valid DSB fill not because of

exceeding way limit.

ACH

08H

DSB_FILL.EXCEED_DSB_LINES DSB Fill encountered > 3 DSB lines.

AEH

01H

ITLB.ITLB_FLUSH

Counts the number of ITLB flushes; includes

4k/2M/4M pages.

B0H

01H

OFFCORE_REQUESTS.DEMAND

_DATA_RD

Demand data read requests sent to uncore.

B0H

04H

OFFCORE_REQUESTS.DEMAND

_RFO

Demand RFO read requests sent to uncore, including

regular RFOs, locks, ItoM.

B0H

08H

OFFCORE_REQUESTS.ALL_DAT

A_RD

Data read requests sent to uncore (demand and

prefetch).

B1H

01H

UOPS_DISPATCHED.THREAD

Counts total number of uops to be dispatched per-

thread each cycle. Set Cmask = 1, INV =1 to count

stall cycles.

PMC0-3 only regardless

HTT.

B1H

02H

UOPS_DISPATCHED.CORE

Counts total number of uops to be dispatched per-

core each cycle.

Do not need to set ANY.

B2H

01H

OFFCORE_REQUESTS_BUFFER

.SQ_FULL

Offcore requests buffer cannot take more entries

for this thread core.

B6H

01H

AGU_BYPASS_CANCEL.COUNT Counts executed load operations with all the

following traits: 1. Addressing of the format [base +

offset], 2. The offset is between 1 and 2047, 3. The

address specified in the base register is in one page

and the address [base+offset] is in another page.

B7H

01H

OFF_CORE_RESPONSE_0

See Section 18.9.5, “Off-core Response

Requires MSR 01A6H.

BBH

01H

OFF_CORE_RESPONSE_1

See Section 18.9.5, “Off-core Response

Requires MSR 01A7H.

BDH

01H

TLB_FLUSH.DTLB_THREAD

DTLB flush attempts of the thread-specific entries.

BDH

20H

TLB_FLUSH.STLB_ANY

Count number of STLB flush attempts.

BFH

05H

L1D_BLOCKS.BANK_CONFLICT

_CYCLES

Cycles when dispatched loads are cancelled due to

L1D bank conflicts with other load ports.

Cmask=1.

C0H

00H

INST_RETIRED.ANY_P

Number of instructions at retirement.

See Table 19-1.

C0H

01H

INST_RETIRED.PREC_DIST

Precise instruction retired event with HW to reduce

effect of PEBS shadow in IP distribution.

PMC1 only; must quiesce

other PMCs.

C1H

02H

OTHER_ASSISTS.ITLB_MISS_R

ETIRED

Instructions that experienced an ITLB miss.

Table 19-13. Non-Architectural Performance Events In the Processor Core Common to 2nd Generation Intel® Core™

i7-2xxx, Intel® Core™ i5-2xxx, Intel® Core™ i3-2xxx Processor Series and Intel® Xeon® Processors E3 and E5 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment