19-42 Vol. 3B

PERFORMANCE-MONITORING EVENTS

19.5.1 Performance Monitoring Events in the Processor Core of Intel Xeon Processor E5 v2

Family and Intel Xeon Processor E7 v2 Family

Non-architectural performance monitoring events in the processor core that are applicable only to Intel Xeon

processor E5 v2 family and Intel Xeon processor E7 v2 family based on the Ivy Bridge-E microarchitecture, with

CPUID signature of DisplayFamily_DisplayModel 06_3EH, are listed in Table 19-12.

F0H

04H

L2_TRANS.CODE_RD

L2 cache accesses when fetching instructions.

F0H

08H

L2_TRANS.ALL_PF

Any MLC or LLC HW prefetch accessing L2, including

rejects.

F0H

10H

L2_TRANS.L1D_WB

L1D writebacks that access L2 cache.

F0H

20H

L2_TRANS.L2_FILL

L2 fill requests that access L2 cache.

F0H

40H

L2_TRANS.L2_WB

L2 writebacks that access L2 cache.

F0H

80H

L2_TRANS.ALL_REQUESTS

Transactions accessing L2 pipe.

F1H

01H

L2_LINES_IN.I

L2 cache lines in I state filling L2.

Counting does not cover

rejects.

F1H

02H

L2_LINES_IN.S

L2 cache lines in S state filling L2.

Counting does not cover

rejects.

F1H

04H

L2_LINES_IN.E

L2 cache lines in E state filling L2.

Counting does not cover

rejects.

F1H

07H

L2_LINES_IN.ALL

L2 cache lines filling L2.

Counting does not cover

rejects.

F2H

01H

L2_LINES_OUT.DEMAND_CLEAN

Clean L2 cache lines evicted by demand.

F2H

02H

L2_LINES_OUT.DEMAND_DIRTY

Dirty L2 cache lines evicted by demand.

F2H

04H

L2_LINES_OUT.PF_CLEAN

Clean L2 cache lines evicted by the MLC prefetcher.

F2H

08H

L2_LINES_OUT.PF_DIRTY

Dirty L2 cache lines evicted by the MLC prefetcher.

F2H

0AH

L2_LINES_OUT.DIRTY_ALL

Dirty L2 cache lines filling the L2.

Counting does not cover

rejects.

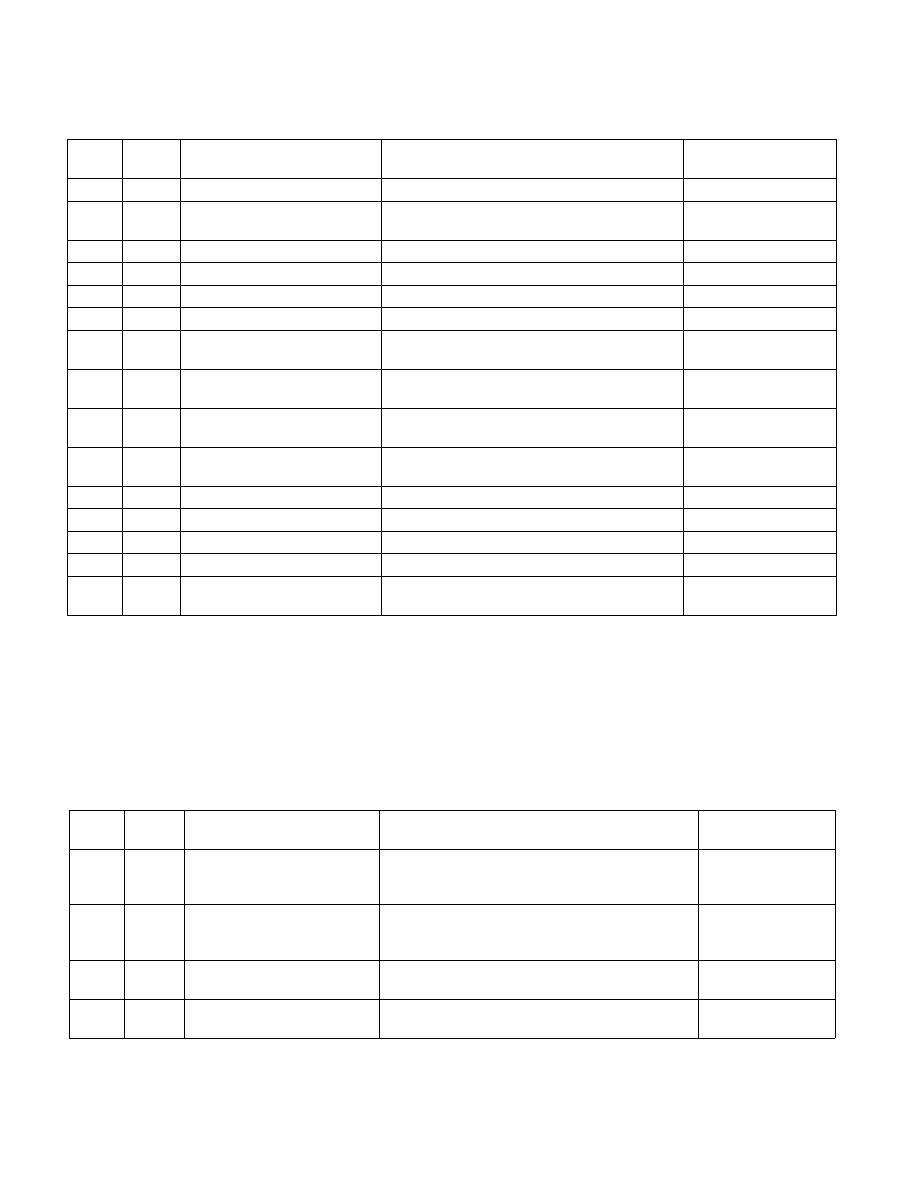

Table 19-12. Non-Architectural Performance Events Applicable Only to the Processor Core of

Intel® Xeon® Processor E5 v2 Family and Intel® Xeon® Processor E7 v2 Family

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

D3H

03H

MEM_LOAD_UOPS_LLC_MISS_R

ETIRED.LOCAL_DRAM

Retired load uops whose data sources were local

DRAM (snoop not needed, Snoop Miss, or Snoop Hit

data not forwarded).

Supports PEBS.

D3H

0CH

MEM_LOAD_UOPS_LLC_MISS_R

ETIRED.REMOTE_DRAM

Retired load uops whose data source was remote

DRAM (snoop not needed, Snoop Miss, or Snoop Hit

data not forwarded).

Supports PEBS.

D3H

10H

MEM_LOAD_UOPS_LLC_MISS_R

ETIRED.REMOTE_HITM

Retired load uops whose data sources were remote

HITM.

Supports PEBS.

D3H

20H

MEM_LOAD_UOPS_LLC_MISS_R

ETIRED.REMOTE_FWD

Retired load uops whose data sources were forwards

from a remote cache.

Supports PEBS.

Table 19-11. Non-Architectural Performance Events In the Processor Core of

3rd Generation Intel® Core™ i7, i5, i3 Processors (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment