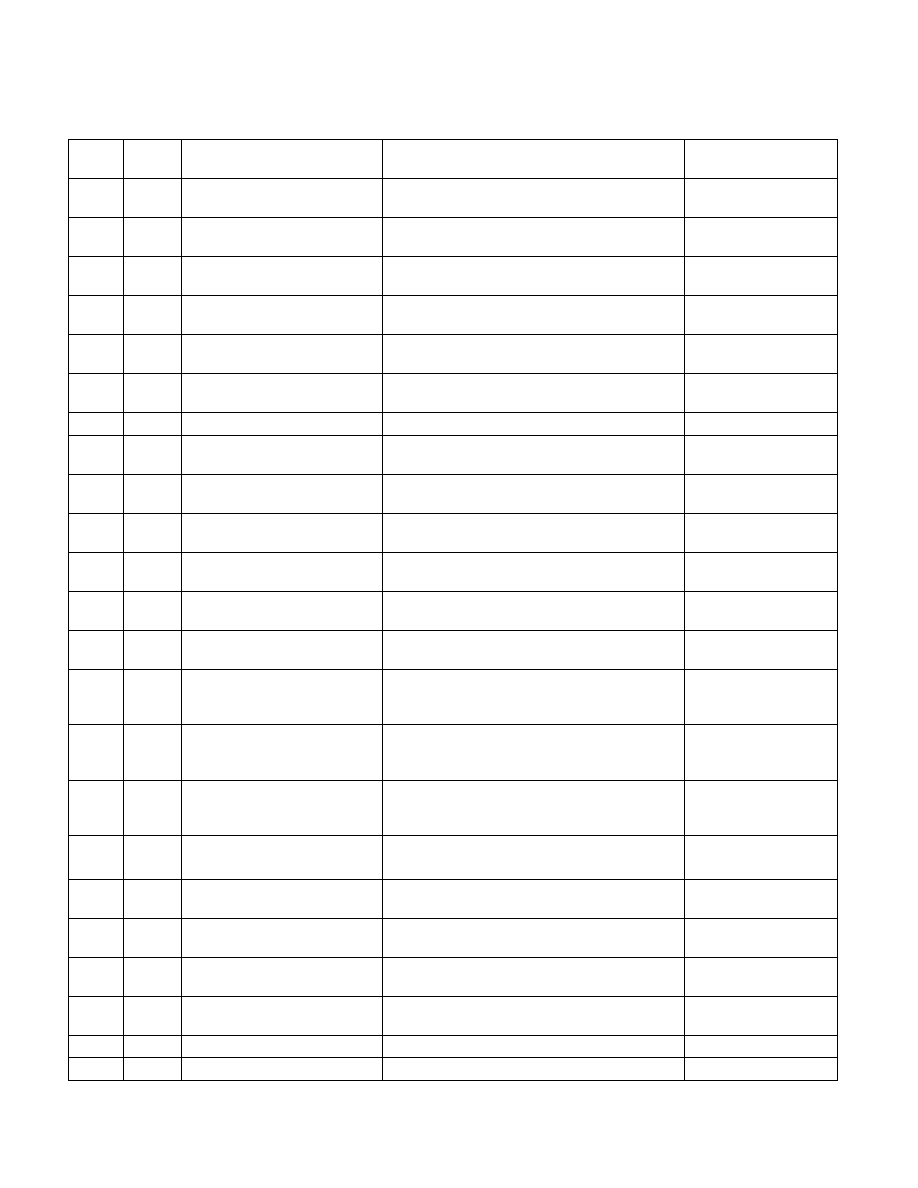

Vol. 3B 19-41

PERFORMANCE-MONITORING EVENTS

CDH

02H

MEM_TRANS_RETIRED.PRECISE_

STORE

Sample stores and collect precise store operation

via PEBS record. PMC3 only.

D0H

11H

MEM_UOPS_RETIRED.STLB_MISS

_LOADS

Retired load uops that miss the STLB.

Supports PEBS.

D0H

12H

MEM_UOPS_RETIRED.STLB_MISS

_STORES

Retired store uops that miss the STLB.

Supports PEBS.

D0H

21H

MEM_UOPS_RETIRED.LOCK_LOA

DS

Retired load uops with locked access.

Supports PEBS.

D0H

41H

MEM_UOPS_RETIRED.SPLIT_LOA

DS

Retired load uops that split across a cacheline

boundary.

Supports PEBS.

D0H

42H

MEM_UOPS_RETIRED.SPLIT_STO

RES

Retired store uops that split across a cacheline

boundary.

Supports PEBS.

D0H

81H

MEM_UOPS_RETIRED.ALL_LOADS All retired load uops.

Supports PEBS.

D0H

82H

MEM_UOPS_RETIRED.ALL_STORE

S

All retired store uops.

Supports PEBS.

D1H

01H

MEM_LOAD_UOPS_RETIRED.L1_

HIT

Retired load uops with L1 cache hits as data

sources.

Supports PEBS.

D1H

02H

MEM_LOAD_UOPS_RETIRED.L2_

HIT

Retired load uops with L2 cache hits as data

sources.

Supports PEBS.

D1H

04H

MEM_LOAD_UOPS_RETIRED.LLC_

HIT

Retired load uops whose data source was LLC hit

with no snoop required.

Supports PEBS.

D1H

08H

MEM_LOAD_UOPS_RETIRED.L1_

MISS

Retired load uops whose data source followed an

L1 miss.

Supports PEBS.

D1H

10H

MEM_LOAD_UOPS_RETIRED.L2_

MISS

Retired load uops that missed L2, excluding

unknown sources.

Supports PEBS.

D1H

20H

MEM_LOAD_UOPS_RETIRED.LLC_

MISS

Retired load uops whose data source is LLC miss.

Supports PEBS.

Restricted to counters 0-

3 when HTT is disabled.

D1H

40H

MEM_LOAD_UOPS_RETIRED.HIT_

LFB

Retired load uops which data sources were load

uops missed L1 but hit FB due to preceding miss to

the same cache line with data not ready.

Supports PEBS.

D2H

01H

MEM_LOAD_UOPS_LLC_HIT_RETI

RED.XSNP_MISS

Retired load uops whose data source was an on-

package core cache LLC hit and cross-core snoop

missed.

Supports PEBS.

D2H

02H

MEM_LOAD_UOPS_LLC_HIT_RETI

RED.XSNP_HIT

Retired load uops whose data source was an on-

package LLC hit and cross-core snoop hits.

Supports PEBS.

D2H

04H

MEM_LOAD_UOPS_LLC_HIT_RETI

RED.XSNP_HITM

Retired load uops whose data source was an on-

package core cache with HitM responses.

Supports PEBS.

D2H

08H

MEM_LOAD_UOPS_LLC_HIT_RETI

RED.XSNP_NONE

Retired load uops whose data source was LLC hit

with no snoop required.

Supports PEBS.

D3H

01H

MEM_LOAD_UOPS_LLC_MISS_RE

TIRED.LOCAL_DRAM

Retired load uops whose data source was local

memory (cross-socket snoop not needed or missed).

Supports PEBS.

E6H

1FH

BACLEARS.ANY

Number of front end re-steers due to BPU

misprediction.

F0H

01H

L2_TRANS.DEMAND_DATA_RD

Demand Data Read requests that access L2 cache.

F0H

02H

L2_TRANS.RFO

RFO requests that access L2 cache.

Table 19-11. Non-Architectural Performance Events In the Processor Core of

3rd Generation Intel® Core™ i7, i5, i3 Processors (Contd.)

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment